# AXIe 1.0: Base Architecture Specification

**Revision 1.0**

June 30, 2010

# **Important Information**

AXIe 1.0 Base Architecture Specification is authored by the AXIe Consortium companies. For a vendor membership roster list, please contact <u>execdir@axiestandard.org.</u>

The AXIe Consortium wants to receive your comments on this specification. To provide such feedback, or to join the consortium, contact <u>execdir@axiestandard.org</u>.

#### Warranty

The AXIe Consortium and its member companies make no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. and its member companies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### Trademarks

PICMG and AdvancedTCA are registered trademarks of the PCI Industrial Computers Manufacturers Group.

PCI-SIG, PCI Express, and PCIe are registered trademarks of PCI-SIG.

LXI is a trademark of the LXI Consortium Inc.

PXI is a trademark of the PXI Systems Alliance.

Other product and company names listed are trademarks or trade names of their respective companies.

No investigation has been made of common-law trademark rights in any work.

| Important Infor                                                                        | mation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Warranty                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                            |

| Trademarks                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                            |

| List of Figures                                                                        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                            |

| List of Tables                                                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                            |

| AXIe 1.0 Base A                                                                        | Architecture Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                          |

| 1.1 Introduction<br>1.2 Audience of<br>1.3 Organization<br>1.4 Architecture<br>1.4.1 A | Specification         of Specification         Overview         dvancedTCA <sup>®</sup> Features         1.4.1.1 AdvancedTCA <sup>®</sup> Overview         1.4.1.2 AdvancedTCA <sup>®</sup> Features Included in AXIe         1.4.1.3 Differences from AdvancedTCA <sup>®</sup> XIe Extensions to AdvancedTCA <sup>®</sup> 1.4.2.1 AXIe Trigger Bus         1.4.2.2 AXIe Timing Interface         1.4.2.3 AXIe Local Bus         1.4.2.4 Future Zone 3 Extensions         1.4.2.5 Alternate Hub 2 Use         1.4.2.6 Additional Electronic Keying | $\begin{array}{c} & & 8 \\ & & 10 \\ & & 10 \\ & & 10 \\ & & 11 \\ & & 11 \\ & & 11 \\ & & 11 \\ & & 11 \\ & & 11 \\ & & 11 \\ & & 11 \\ & & 12 \\ & & 13 \\ & & 14 \\ & & 14 \\ & & 14 \\ & & 14 \\ & & 14 \\ & & 14 \\ & & 15 \\ & & 15 \\ & & 16 \\ & & 16 \end{array}$ |

| 1.6 References<br>1.7 Terminology<br>1.7.1 A<br>1.7.2 A<br>1.7.3 A                     | 1.4.2.7 Additional System Management Requirements<br>1.4.2.8 Internal EMC Requirements<br>e Requirements<br>XIE Terms<br>dvancedTCA <sup>®</sup> Terms Applicable to AXIe<br>dvancedTCA <sup>®</sup> Terms Not Applicable to AXIe                                                                                                                                                                                                                                                                                                                  | 16<br>16<br>16<br>16<br>16<br>16<br>17<br>18                                                                                                                                                                                                                               |

| AXIe 1.0 Revision 1.0, June                                                            | 30, 2010 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AXIe Consortium                                                                                                                                                                                                                                                            |

AXIe Consortium

| <b>Z</b> . F | XIe Mechanical Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | 2.1 General Mechanical Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|              | 2.2 AXIe Module Mechanical Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|              | 2.2.1 AXIe Front Panel LEDs and Labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|              | 2.3 Rear Transition Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|              | 2.4 AXIe Backplane Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|              | 2.4.1 Zone 1 Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|              | 2.4.2 Zone 2 Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|              | 2.4.3 Zone 3 Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|              | 2.4.4 Alignment and Keying                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|              | 2.5 Backplanes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|              | 2.6 Subracks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|              | 2.7 AXIe Chassis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 3. H         | lardware Platform Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25 |

| ••••         | 3.1 Electronic Keying                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|              | 3.1.1 Electronic Keying Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|              | 3.1.2 Point-to-Point Link Connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|              | 3.1.3 Backplane Point-to-Point Link Connectivity Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|              | 3.1.4 Board Point-to-Point Connectivity Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|              | 3.1.5 PCI Express <sup>®</sup> Electronic Keying                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|              | 3.1.6 AXIe Timing Interface Electronic Keying                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31 |

|              | 3.1.7 AXIe Local Bus Electronic Keying                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31 |

|              | 3.1.8 Set AXIe Port State Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32 |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|              | 3 1 9 Get A X le Port State Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12 |

|              | 3.1.9 Get AXIe Port State Command<br>3.2 Intelligent Platform Management Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4. F         | 3.2 Intelligent Platform Management Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|              | 3.2 Intelligent Platform Management Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|              | 3.2 Intelligent Platform Management Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Thermal Requirements<br>Data Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Thermal Requirements<br>Data Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Thermal Requirements<br>Data Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements<br>Data Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Thermal Requirements<br>Data Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.1 Base Interface Topology<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Thermal Requirements<br>Data Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.1 Base Interface Topology<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology                                                                                                                                                                                                                                                                                                  |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Thermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.1 Base Interface Topology<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology<br>6.2.1.4 AXIe Timing Interface Topology                                                                                                                                                                                                                                                        |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.1 Base Interface Topology<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology<br>6.2.1.4 AXIe Timing Interface Topology<br>6.2.1.5 AXIe Trigger Bus Topology                                                                                                                                                                                                                   |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology                                                                                                                                                                                                                                                                                                                                     |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Thermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.1 Base Interface Topology<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology<br>6.2.1.4 AXIe Timing Interface Topology<br>6.2.1.5 AXIe Trigger Bus Topology<br>6.2.2 AXIe Zone 2 Routing Requirements                                                                                                                                                                         |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.1 Base Interface Topology<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology<br>6.2.1.4 AXIe Timing Interface Topology<br>6.2.1.5 AXIe Trigger Bus Topology<br>6.2.3 AXIe Zone 2 Routing Requirements<br>6.3 Module Requirements                                                                                                                                              |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Thermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors.<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology<br>6.2.1.4 AXIe Timing Interface Topology<br>6.2.1.5 AXIe Trigger Bus Topology<br>6.2.3 AXIe Zone 2 Routing Requirements<br>6.3 Module Requirements<br>6.3 I System Modules<br>6.3.1 Instrument Modules<br>6.3.3 Instrument Hub Modules                                                                                            |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1.1 Base Interface Topology<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology<br>6.2.1.4 AXIe Timing Interface Topology<br>6.2.1.5 AXIe Trigger Bus Topology<br>6.2.1.5 AXIe Zone 2 Routing Requirements<br>6.2.3 AXIe Zone 2 Electrical Requirements<br>6.3 Module Requirements<br>6.3.1 System Modules<br>6.3.2 Instrument Modules                                           |    |

| 5. 1         | 3.2 Intelligent Platform Management Bus<br>Power Distribution<br>Fhermal Requirements<br>Data Transport<br>6.1 Zone 2 Connectors<br>6.2 Backplane Requirements<br>6.2.1 Backplane Topologies<br>6.2.1 Backplane Topologies<br>6.2.1.2 Fabric Interface Topology<br>6.2.1.3 AXIe Local Bus Topology<br>6.2.1.4 AXIe Timing Interface Topology<br>6.2.1.5 AXIe Trigger Bus Topology<br>6.2.2 AXIe Zone 2 Routing Requirements<br>6.3 Module Requirements<br>6.3 I System Modules<br>6.3.1 System Modules<br>6.3.4 Zone 2 Support Requirements for Modules<br>6.3.4 Zone 2 Support Requirements for Modules |    |

AXIe Consortium

4

AXIe 1.0 Revision 1.0, June 30, 2010

| 6.4 Zone 2 Connector Usage                              | 41 |

|---------------------------------------------------------|----|

| 6.4.1 System Module/Slot Zone 2 Pin Assignments         |    |

|                                                         |    |

| 6.4.2 Instrument Module/Slot Zone 2 Pin Assignments     |    |

| 6.4.3 Instrument Hub Module/Slot Zone 2 Pin Assignments | 43 |

| 6.5 Base Interface                                      | 44 |

| 6.6 Fabric Interface Requirements                       | 45 |

| 6.7 AXIe Timing Interface Requirements                  | 46 |

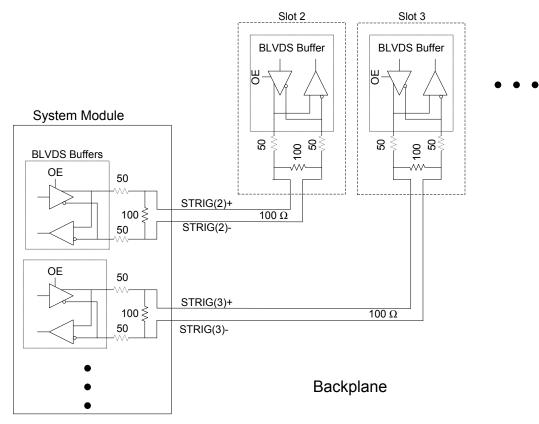

| 6.7.1 STRIG                                             | 46 |

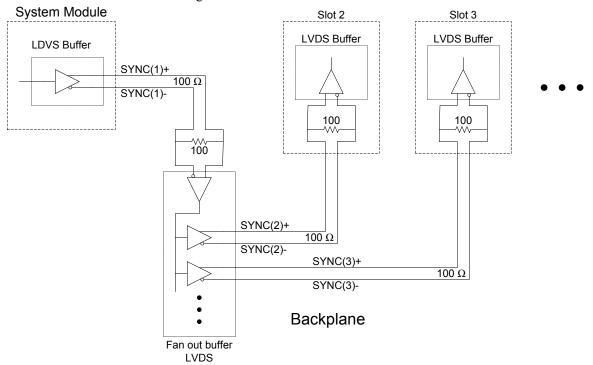

| 6.7.2 SYNC                                              | 48 |

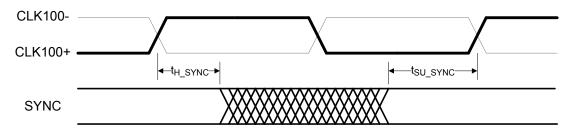

| 6.7.3 CLK100                                            | 49 |

| 6.7.4 FCLK                                              | 50 |

| 6.8 AXIe Trigger Bus Requirements                       |    |

| 6.9 AXIe Local Bus                                      |    |

|                                                         |    |

| 7. Electromagnetic Compatibility (EMC)                                | 54 |

|-----------------------------------------------------------------------|----|

| 7.1 Conducted EMC                                                     |    |

| 7.1.1 Chassis and Power Supply Conducted Emissions and Susceptibility |    |

| 7.1.2 Module Conducted Emissions                                      | 55 |

| 7.1.3 Module Conducted Susceptibility                                 |    |

| 7.2 Radiated EMC                                                      |    |

| 7.2.1 Radiated Emissions                                              |    |

| 7.2.2 Radiated Susceptibility                                         |    |

| 7.2.3 Regulatory Compliance                                           | 59 |

| 7.3 EMC Test Methods                                                  | 59 |

| 8. AXIe Software Requirements | 60 |

|-------------------------------|----|

|-------------------------------|----|

| 9. Appendix A: AXIe Trademark and Logo Usage                      | 61 |

|-------------------------------------------------------------------|----|

| 9.1 Definitions:                                                  |    |

| 9.2 Usage Conventions                                             |    |

| 9.3 Trademark Use Standards                                       |    |

| 9.3.1 Logo Mark                                                   |    |

| 9.3.2 The AXIe Trademark and the AXIe Consortium Name Use in Text |    |

| 9.3.3 AXIe Logo for Product Labeling                              |    |

| 9.4 Logo Use Standards                                            |    |

| 9.4.1 Scale                                                       |    |

| 9.4.2 Clear Space                                                 |    |

| 9.4.3 Color Treatments                                            |    |

| 9.4.4 Approved Formats                                            |    |

| 9.5 Application Examples                                          |    |

| 9.5.1 Acceptable Usage                                            |    |

| 9.5.2 Product Usage                                               | 64 |

| 9.5.3 Unacceptable Usage                                          |    |

## List of Figures

| Figure 1-1: AXIe chassis and module                              |                        |                 |

|------------------------------------------------------------------|------------------------|-----------------|

| Figure 1-2: AXIe chassis block diagram.                          |                        | 9               |

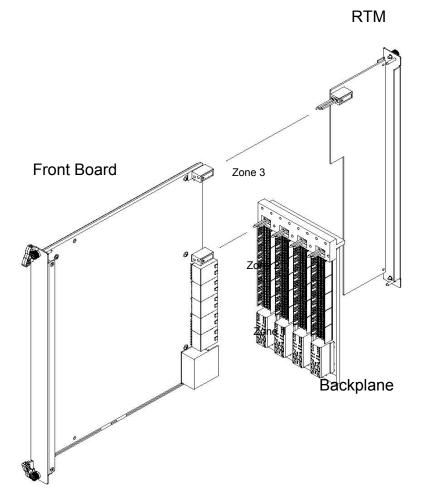

| Figure 1-3: AdvancedTCA <sup>®</sup> front board, backplane, and | RTM                    |                 |

| Figure 1-4: AdvancedTCA <sup>®</sup> front board                 |                        |                 |

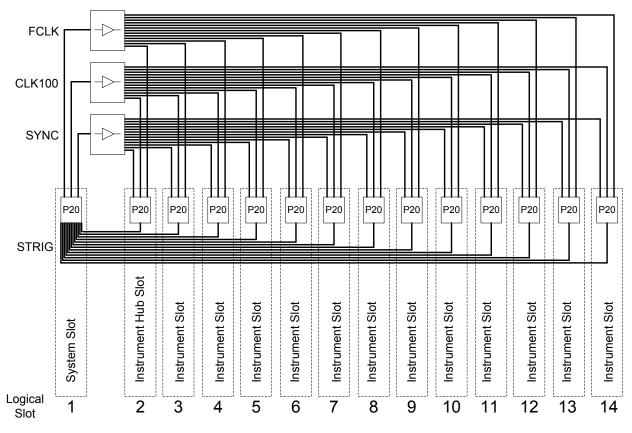

| Figure 1-5: AXI timing interface.                                |                        |                 |

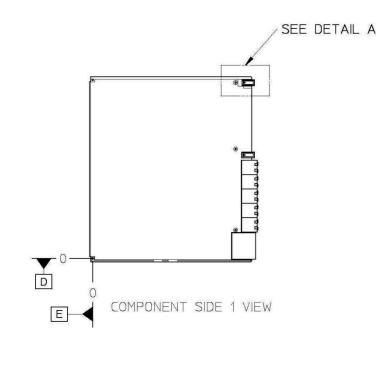

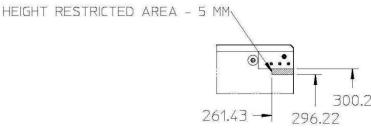

| Figure 2-1: Additional component height restriction area         | a for AXIe 1.0 modules |                 |

| AXIe 1.0 Revision 1.0, June 30, 2010                             | 5                      | AXIe Consortium |

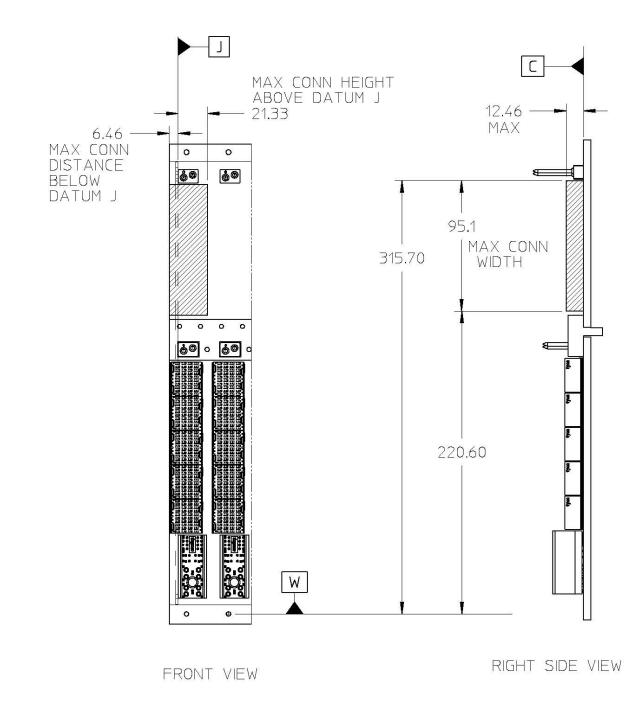

| Figure 2-2: | AXIe zone 3 midplane connector envelope                                      |                           |

|-------------|------------------------------------------------------------------------------|---------------------------|

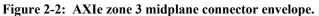

|             | AXIe local bus backplane topology                                            |                           |

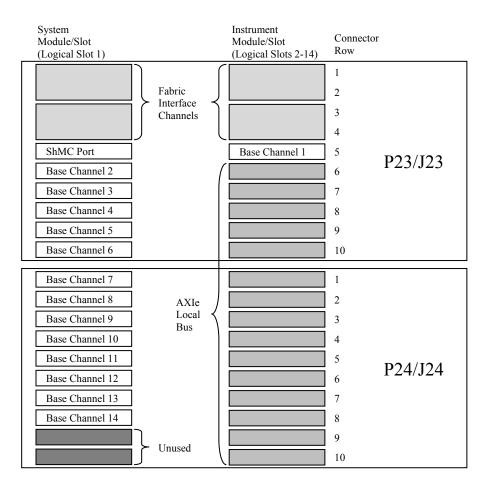

| Figure 6-2: | Base Interface Channel Assignments                                           | 45                        |

|             | Typical STRIG Implementation                                                 |                           |

| Figure 6-4: | Typical SYNC backplane and module implementation.                            |                           |

| Figure 6-5: | Synchronous operation of the SYNC signal.                                    |                           |

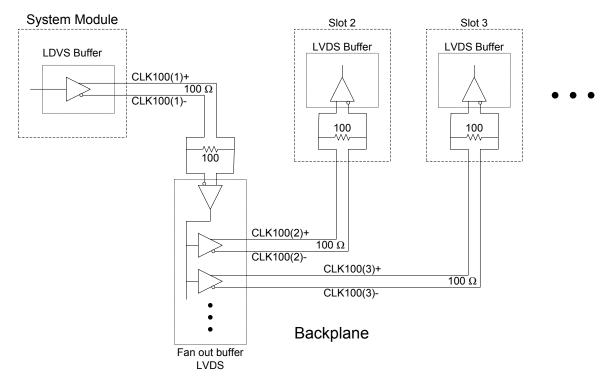

| Figure 6-6: | Typical CLK100 backplane and module implementation.                          |                           |

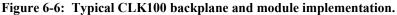

| Figure 6-7: | Typical backplane and module FCLK implementation.                            | 51                        |

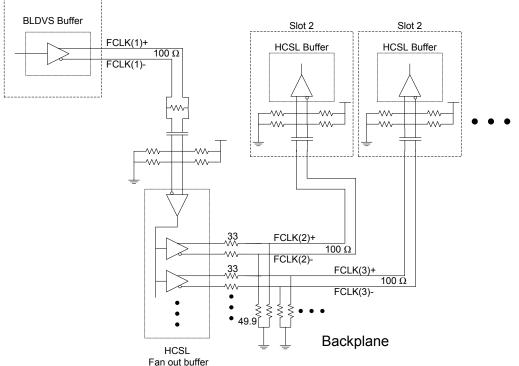

| Figure 6-8: | Typical AXIe trigger bus implementation.                                     |                           |

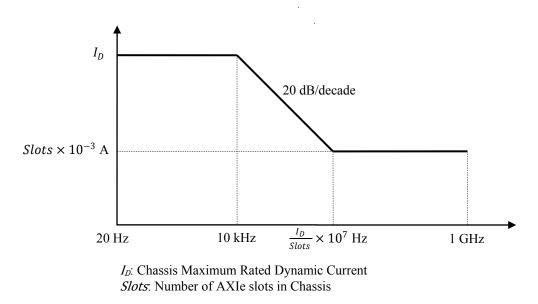

| Figure 7-1: | Chassis Load Current.                                                        | 54                        |

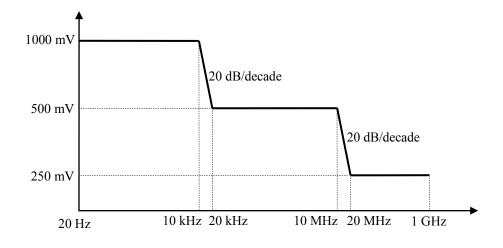

| Figure 7-2: | Chassis total induced noise and ripple                                       | 55                        |

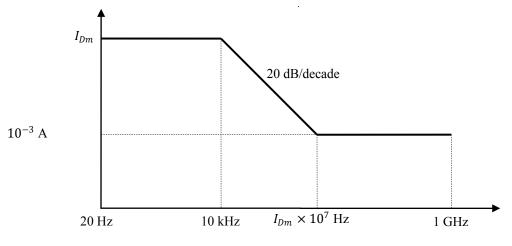

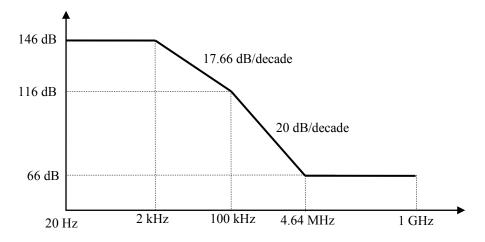

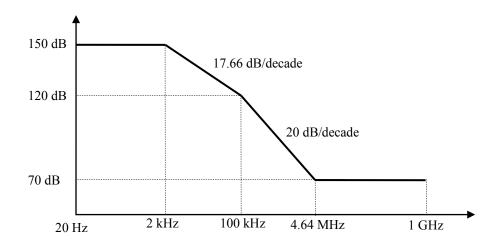

| Figure 7-3: | Module Conducted Emissions.                                                  |                           |

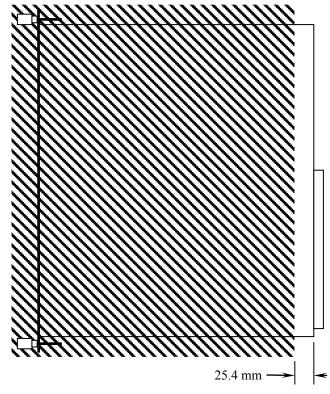

| Figure 7-4: | Module radiated emissions test area.                                         |                           |

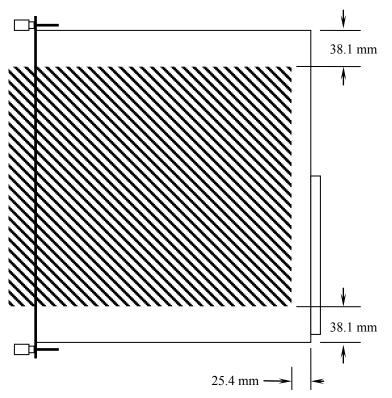

| Figure 7-5: | Module close field radiated emissions limit (dB above 1 picoTesla)           | 57                        |

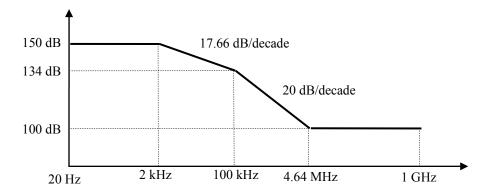

| Figure 7-6: | Module radiated susceptibility limits near top and bottom edges (dB above 1) | picoTesla)57              |

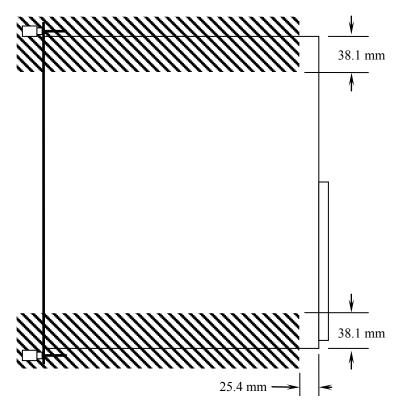

| Figure 7-7: | Module edge radiated susceptibility test area.                               |                           |

| Figure 7-8: | Module radiated susceptibility limits (dB above 1 picoTesla).                |                           |

| Figure 7-9: | Module center radiated susceptibility test area                              | 59                        |

| Figure 9-1: | AXIe logo                                                                    | 61                        |

| Figure 9-2: | Various sizes of the AXIe logo                                               |                           |

|             | Required clear space around the AXIe logo.                                   |                           |

| Figure 9-4: | Pantone 7477 C and black AXIe logos                                          | 63                        |

| Figure 9-5: | Examples of unacceptable AXIe logo usage Err                                 | or! Bookmark not defined. |

#### List of Tables

| Table 1-1. Architecture Specification Revisions                                                              | 7    |

|--------------------------------------------------------------------------------------------------------------|------|

| Table 3-1: AXIe point-to-point channel attributes.                                                           |      |

| Table 3-2: AXIe Backplane Point-to-Point Connectivity Record.                                                | 27   |

| Table 3-3: AXIe Point-to-Point Slot Descriptor                                                               |      |

| Table 3-4: AXIe Point-to-Point Channel Descriptor                                                            | 27   |

| Table 3-5: AXIe Board Point-to-Point Connectivity Record.                                                    | 28   |

| Table 3-6: AXIe Link Descriptor.                                                                             | 28   |

| Table 3-7: AXIe Link Designator.                                                                             | 29   |

| Table 3-8: AXIe Link Type                                                                                    | 29   |

| Table 3-9: AXIe Link Type Extension values when the AXIe Interface Type is 00b (Fabric Interface) and the AX | XIe  |

| Link Type is 01h (AXIe PCIe <sup>®</sup> ).                                                                  | 29   |

| Table 3-10: AXIe Link Type Extension values when the AXIe Interface Type is 10b (Timing Interface) and the   | AXIe |

| Link Type is 02h (AXIe FCLK), 03h (AXIe FCLK), or 04h (AXIe FCLK).                                           | 29   |

| Table 3-11: AXIe Link Type Extension values when the AXIe Interface Type is 10b (Timing Interface) and the   | AXIe |

| Link Type is 05h (AXIe STRIG).                                                                               | 29   |

| Table 3-12: AXIe Link Type Extension values when the AXIe Interface Type is 01b (AXIe Local Bus Interface    |      |

| Table 3-13: PCIe port and backplane channel compatibility.                                                   |      |

| Table 3-14: Set AXIe Port State Command.                                                                     |      |

| Table 3-15: Get AXIe Port State command.                                                                     |      |

| Table 6-1: J20/P20 Pin assignments for the system slot (logical slot 1).                                     | 42   |

| Table 6-2: J20/P20 Pin assignments for instrument slots (logical slots 2-14).                                | 42   |

| Table 6-3: J21/P21 Pin assignments for instrument slots (logical slots 2-14).                                | 43   |

| Table 6-4: J23/P23 Pin assignments for instrument slots (logical slots 2-14).                                |      |

| Table 6-5: J24/P24 Pin assignments for instrument slots (logical slots 2-14).                                | 43   |

| Table 6-6: J20/P20 Pin assignments for instrument hub slot (logical slots 2) in 14 slot backplane            |      |

| Table 6-7 : System module SYNC and CLK100 output timing for synchronous operation.                           | 49   |

| Table 6-8: Instrument module SYNC and CLK100 input timing for synchronous operation                          |      |

| Table 9-1: Pantone 7477 C color specifications                                                               | 63   |

# **AXIe 1.0 Base Architecture Specification**

# **Revision History**

This section is an overview of the revision history of the AXIe 1.0 specification.

| <b>Revision Number</b> | Date of Revision | <b>Revision Notes</b> |

|------------------------|------------------|-----------------------|

| 1.0                    | June 30, 2010    | Initial Version       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

|                        |                  |                       |

| Table 1-1 | Architecture | Specification | Revisions |

|-----------|--------------|---------------|-----------|

|           | Alchilcoluic | opeometation  | 110113    |

## 1. Overview of the AXIe Base Specification

#### 1.1 Introduction

The AXIe Base Architecture defines an extensible platform for general purpose, modular instrumentation. The architecture incorporates the best features of earlier modular open instrumentation platforms, including VXIbus, PXI, and LXI. Like VXIbus and PXI, the architecture is based on a popular modular computing platform with added features important to developers and users of test and measurement systems. The base platform is AdvancedTCA<sup>®</sup>, an open architecture for modular computing components targeted for communications infrastructure applications. The AdvancedTCA<sup>®</sup> architecture includes provisions for power distribution, power and system management, Ethernet communication between modules, and PCI Express<sup>®</sup> communication between modules, along with other capabilities. The AXIe Base Architecture includes some modifications to the AdvancedTCA<sup>®</sup> architecture. These modifications provide timing, triggering, and module-to-module data movement features that are important to the implementation of high-performance test and measurement systems. These modifications are designed to allow most AdvancedTCA<sup>®</sup> computing boards to work within an AXIe 1.0 environment, to allow many general-purpose AXIe devices to work in AdvancedTCA<sup>®</sup> environments, and to prevent any damaging incompatibilities between AXIe and AdvancedTCA<sup>®</sup> devices and system components.

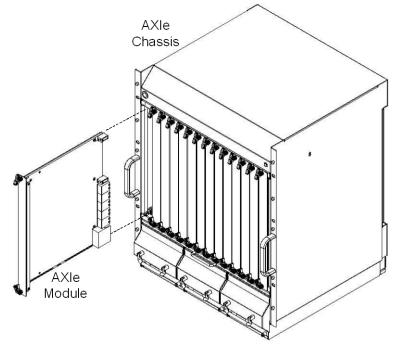

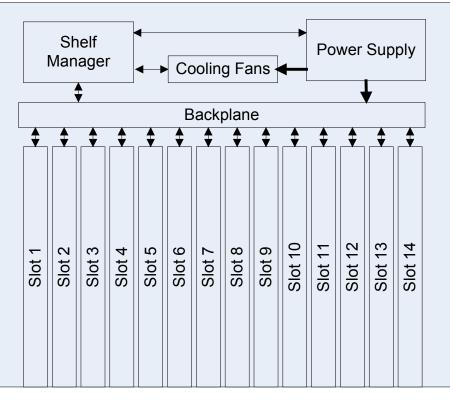

AXIe, like other modular instrumentation platform specifications, defines a set of mechanical, electrical, and logical interfaces between instrumentation *modules* and *chassis*. A typical AXIe chassis and module are illustrated in Figure 1-1, and a simplified chassis block diagram is shown in Figure 1-2. AXIe modules slide into slots in the chassis' front subrack, and engage connectors on the backplane. The backplane provides power and system management connections to the modules, and control, data, trigger, and timing connections between the modules. The shelf manager is a dedicated system management controller that monitors the health of the chassis subsystems and modules, controls the chassis cooling fans, and manages the chassis power-up sequence. The modules house various functions related to the test/measurement application, including (but not limited to) signal measurement, signal sources, digital IO, data communication, signal analysis, and general purpose computing. All external IO in an AXIe 1.0 system is through connectors on the front faceplates of the AXIe modules.

Figure 1-1: AXIe chassis and module.

AXIe Consortium

The AXIe backplane supports two serial interface standards, LAN and PCI Express<sup>®</sup>. Both interfaces are suitable for module control and measurement data transfer. Most AXIe modules support one or the other of these interfaces. A few modules may connect to both interfaces. The LAN interface is best suited to intelligent modules that support high-level command interfaces. These LAN connected AXIe modules are expected to conform to many of the LXI protocols and usability requirements as specified by the AXIe 2.0 Software Specification. The PCI Express<sup>®</sup> interface is best suited for less intelligent modules that require low-level register control. These PCI Express<sup>®</sup> modules operate as extensions of the host computer and appear to the host operating system as standard PCI Express<sup>®</sup> peripherals. In addition, these modules are required to conform to most of the PXI software requirements, as defined by the AXIe 2.0 Software Specification. Thus the integration, programming, and use models of both types of modules are already familiar to most test system integrators and users.

**Chassis Front**

AXIe modules are ~320 mm tall, ~280 mm deep, and ~30 mm wide. They each typically dissipate 100 - 200 W of power. The large board area, module volume, and high power capability make the AXIe platform especially well suited for applications that require large channel counts, high performance measurements, and/or efficient use of rack space.

The AXIe 1.0 specification defines a general-purpose test and measurement platform. Related AXIe 3.n specifications may define extensions to the AXIe 1.0 architecture optimized for particular market segments. The AXIe 3.1 specification defines extensions optimized for semiconductor test systems.

## 1.2 Audience of Specification

This specification is primarily for the use of AXIe equipment manufacturers and system integrators who are implementing products and systems that conform to the requirements of this specification. The primary audience is assumed to have extensive knowledge of modular measurement hardware architectures, and access to the various referenced technical specifications. However, this specification should also prove useful to managers and anyone else involved in the selection of modular test system platforms and architectures.

## 1.3 Organization of Specification

This specification consists of a system of numbered RULES, RECOMMENDATIONS, PERMISSIONS, and OBSERVATIONS, along with supporting text, tables, and figures.

**RULE**s outline the core requirements of the specification. They are characterized by the keyword "**SHALL**". Conformance to these rules provides the necessary level of compatibility to support the multi-vendor interoperability expected by system integrators and end users in the test and measurement industry. Products that conform to this specification must meet all of the requirements spelled out in the various rules.

**RECOMMENDATIONs** provide additional guidance that will help AXIe equipment manufacturers improve their users' experiences with AXIe systems. They are characterized by the keyword "**SHOULD**". Following the recommendations should improve the functionality, flexibility, interoperability, and/or usability of AXIe products. Products are not required to implement the recommendations.

**PERMISSIONs** explicitly highlight some of the flexibility of the AXIe specification. They are characterized by the keyword "**MAY**". The permissions generally clarify the range of design choices that are available to product and system designers at their discretion. They allow designers to trade off functionality, cost, and other factors in order to produce products that meet their users' expectations. Permissions are neutral and imply no preference as to their implementation.

**OBSERVATION**s explicitly highlight some of the important nuances of the specification. They help the readers to fully understand some of the implications of the specification's requirements and/or the rationale behind particular requirements. They generally provide valuable design guidance.

All rules, recommendations, permissions, and observations must be considered in the context of the surrounding text, tables, and figures. Rules may explicitly or implicitly incorporate information from the text, tables, and figures. Although the authors of this specification have gone to significant effort to insure that all of the necessary requirements are spelled out in the rules, it is possible that some important requirements appear only in the specification's free text. Conservative design practice dictates that such embedded requirements be treated as rules.

The AXIe 1.0 specification is based on the AdvancedTCA<sup>®</sup> specification. The relevant AdvancedTCA<sup>®</sup> numbered requirements are explicitly referenced in this specification's rules, recommendations, permissions, and observations. These requirements are incorporated along with their supporting context (text, tables, figures, etc.). Any AdvancedTCA<sup>®</sup> numbered requirement that is not explicitly included by this specification's rules, recommendations, permissions, or observations, is excluded from the AXIe 1.0 requirements.

Successful implementation of AXIe products and systems requires in-depth knowledge of this AXIe 1.0 specification and the AdvancedTCA<sup>®</sup> specification. This specification does not reproduce any content from the AdvancedTCA<sup>®</sup> specification, beyond the high-level description in Section 1.4.1.1"AdvancedTCA<sup>®</sup> Overview".

## 1.4 Architecture Overview

The AXIe architecture consists of hardware and software requirements that support the smooth multi-vendor integration of AXIe modules and chassis into powerful test systems. The architectural foundation of AXIe is the AdvancedTCA<sup>®</sup> specification which defines a modular platform optimized for telecom central office applications. AXIe adds several hardware and software features that are important to the test and measurement marketplace.

## 1.4.1 AdvancedTCA<sup>®</sup> Features

The AXIe architecture is based largely on the AdvancedTCA<sup>®</sup> architecture and incorporates many of its features. The following sections provide a brief overview of the AdvancedTCA<sup>®</sup> architecture and a summary of the features that the AXIe architecture includes and excludes.

## 1.4.1.1 AdvancedTCA® Overview

The AdvancedTCA<sup>®</sup> specification defines an open architecture for modular computing components for highavailability network and telecom service installations. The basic mechanical elements are front boards, rear transition modules (RTMs), backplanes, and subracks. The front boards provide the core system functionality, while the RTMs provide user-defined external IO connections through the rear of the system. The backplane provides connector interfaces for both front board IO and power distribution, while the subrack provides the mechanical support of the front boards and RTMs. A single backplane and subrack may support up to 16 front boards (and matching RTMs). Figure 1-3 illustrates the physical relationships between front boards, backplanes, and RTMs.

Figure 1-3: AdvancedTCA<sup>®</sup> front board, backplane, and RTM.

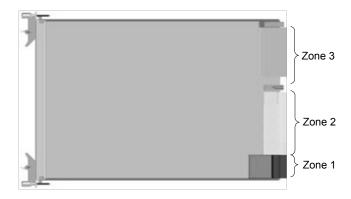

The front board, shown in Figure 1-4, is 322.75 mm tall, 30.48 mm wide, and about 280 mm deep. It includes a front face plate with injector/ejector handles. The backplane connector region is divided into 3 zones. Zone 1 includes power and platform management signals. Zone 2 includes data transport signals, and Zone 3 includes IO signals to the RTM.

AXIe 1.0 Revision 1.0, June 30, 2010

#### Figure 1-4: AdvancedTCA<sup>®</sup> front board.

AdvancedTCA<sup>®</sup> includes an extensive platform management system that includes a central shelf manager and distributed management controllers. The system monitors the health of the system, manages the system power and cooling, and oversees the compatibility of the module interconnects. The AdvancedTCA<sup>®</sup> architecture is designed for 99.999% availability, supported by dual redundancy of critical resources, board hot swap, etc.

Systems are designed to operate from -48 VDC battery power, which is commonly available in telecom central offices. This power is distributed directly to the front boards, using redundant power feeds.

AdvancedTCA<sup>®</sup> includes extensive cooling characterization requirements that enable system integrators to assemble systems in which all components receive adequate cooling.

The zone 2 interconnect includes various interfaces for module-to-module communication. There is a base interface for LAN signaling that is connected in a dual-redundant star topology. There is a similar fabric interface that can be used for a variety of signaling schemes, including PCI Express<sup>®</sup>. It is usually connected in a dual-star topology. Two of the front boards serve as hubs for the base and fabric stars, providing the switching resources necessary for the operation of the base and fabric interface. The fabric interface may support other topologies, including a full mesh. There is also a synchronization clock interface, which provides bused telecom clocks across the backplane, and an update channel interface which provides for proprietary communication between compatible boards. All signal connections in zone 2 are differential pairs.

## 1.4.1.2 AdvancedTCA<sup>®</sup> Features Included in AXIe

The following sections provide a summary of the AdvancedTCA<sup>®</sup> features that are also part of the AXIe architecture.

#### 1.4.1.2.1 Mechanical

The AXIe architecture incorporates all of the AdvancedTCA<sup>®</sup> mechanical requirements for front board assemblies, Zone 1 and Zone 2 backplane connectors, backplanes, and subracks, with only a few exceptions related to the required number of slots, and support of rear transition modules, and environmental requirements. Unlike AdvancedTCA<sup>®</sup>, AXIe systems are often used in laboratory and production environments. These environments are typically different than the central office equipment room environments where AdvancedTCA<sup>®</sup> equipment is usually deployed. These differences may include power delivery systems, ambient temperature range, acoustic limits, EMC, etc. In general, each AXIe equipment manufacturer is responsible for determining and specifying the suitable environmental requirements for its AXIe products.

#### 1.4.1.2.2 Hardware Platform Management

The AXIe architecture incorporates most of the hardware platform management features of AdvancedTCA<sup>®</sup> and requires AXIe devices and system components to comply with all applicable AdvancedTCA<sup>®</sup> hardware platform management requirements, with a few exceptions related to redundancy and telecom-specific functions. The AXIe architecture also incorporates some extensions to the electronic keying scheme in order to support unique AXIe features and requirements.

#### 1.4.1.2.3 Power Distribution

The AXIe architecture incorporates the AdvancedTCA<sup>®</sup> power-distribution scheme for backplanes and front boards, with exceptions related to redundancy and the distributed voltage tolerance range. Advanced TCA<sup>®</sup> is targeted for applications that are powered from external 48V battery plants. AXIe products are typically used in locations where the primary power source is the local AC power mains. Thus a typical AXIe chassis will include a power supply unit (PSU) that converts a range of AC line voltages/frequencies to the 48VDC distributed on the AXIe backplane.

#### 1.4.1.2.4 Thermal

The AXIe architecture incorporates the AdvancedTCA<sup>®</sup> thermal requirements for front boards and shelf front board slots. Typical AXIe applications don't require the cooling system redundancy that is expected in most Advanced TCA applications.

#### 1.4.1.2.5 Data Transport

The AXIe architecture incorporates the AdvancedTCA<sup>®</sup> requirements for Zone 2 base and fabric interfaces for backplanes and front boards, with exceptions related to redundancy. AXIe systems are limited to a single-star topology for the base interface (LAN) and a dual-star topology for the fabric interface (PCIe<sup>®</sup>/proprietary serial).

## 1.4.1.2.6 PICMG<sup>®</sup> 3.4 PCI Express<sup>®</sup> Fabric

The AXIe architecture incorporates the requirements for the PCI Express<sup>®</sup> fabric interface as defined in the PICMG<sup>®</sup> 3.4 extension to the AdvancedTCA<sup>®</sup> specification.

## 1.4.1.3 Differences from AdvancedTCA®

The following sections provide a summary of the AdvancedTCA<sup>®</sup> features that are excluded from the AXIe architecture.

#### 1.4.1.3.1 No Requirements for Redundancy

The general-purpose test and measurement marketplace does not have the 99.999% availability requirement expected in the telecom marketplace. Thus the AXIe architecture does not require use of the redundancy features specified in AdvancedTCA<sup>®</sup>. Modules and systems may optionally implement the redundant power distribution scheme. Use of the redundant power management bus is not required. The Hub 2 base channels are not routed on AXIe backplanes. The Hub 2 fabric channel use is not defined, and it is available for vendor-specific use.

#### 1.4.1.3.2 No Rear Transition Modules

AXIe 1.0 systems do not use rear transition modules. Measurement I/O signals are routed through the front modules' faceplates. Mainframes are not required to provide rear transition module slots. Subsequent AXIe 3.n specifications may define Zone 3 backplane or rear transition module schemes for particular markets. The AXIe 1.0 module envelopes are defined to prevent AXIe 1.0 modules from interfering with AXIe 3.n zone 3 backplane connectors that fit within a defined envelope.

#### 1.4.1.3.3 Maximum of 14 Slots

General-purpose instrumentation equipment is typically designed for mounting in 19" EIA racks. This allows room for only 14 vertical slots. The AXIe 1.0 architecture permits a maximum of 14 slots in a mainframe, instead of the 16 slots allowed in AdvancedTCA<sup>®</sup> shelves.

#### 1.4.1.3.4 No External Shelf Mechanical, Electrical, or Environmental Requirements

The AXIe architecture is focused on compatibility between modules, backplanes, subracks, and other system components within a chassis. The power source, dimensions, environmental specifications, and regulatory requirements are determined by each AXIe chassis supplier according to market needs.

#### 1.4.1.3.5 Modified Synchronization Clock Interface

The AXIe architecture expands the use of the Synchronization Clock Interface for additional purposes beyond those defined in AdvancedTCA<sup>®</sup>. AXIe backplanes maintain the bused topology of most of the Synchronization Clock signals, and devices implement the same MLVDS signaling levels as AdvancedTCA<sup>®</sup>. However, the bus is used for general-purpose synchronization and triggering by AXIe modules, and AXIe systems do not generally distribute the specific clock signals defined by AdvancedTCA<sup>®</sup> (although such use is permissible within the AXIe architecture).

### 1.4.1.3.6 No Update Channel Interface

The AXIe architecture does not implement the Update Channel Interface as it is defined in AdvancedTCA<sup>®</sup>, which allows a variety of backplane topologies and implementations. AXIe backplanes implement a single bused MLVDS topology for the signals connecting to those Zone 2 connector contacts, and devices implement different signaling schemes as defined in this specification. AXIe devices and system components implement electronic keying appropriate to prevent incompatible connections between AXIe and AdvancedTCA<sup>®</sup> devices installed in either system environment.

## 1.4.2 AXIe Extensions to AdvancedTCA®

The AXIe architecture provides several features not found in AdvancedTCA<sup>®</sup>. It also places additional restrictions on modules and system components in order to assure a higher level of interoperability. The following sections summarize these features and restrictions.

## 1.4.2.1 AXIe Trigger Bus

One obvious differentiating feature is the AXIe Trigger Bus, TRIG[0-11], which consists of 12 MLVDS trigger pairs bused across all of the slots on an AXIe backplane. This bus (together with the AXIe Timing Interface and Local Bus) is implemented using the Zone 2 connector contact positions that are used for the Update Channel, Synchronization Clock, and Slot 15 and 16 fabric channels in AdvancedTCA<sup>®</sup>.

## 1.4.2.2 AXIe Timing Interface

Another obvious differentiating feature is the AXIe Timing Interface, which includes star clock (CLK100), star synchronization (SYNC), star trigger (STRIG), and fabric clock (FCLK) signals. This interface is implemented using some of the Zone 2 connector contact positions that are used for the Update Channel, Synchronization Clock, and Slot 15 and 16 Data fabric channels in AdvancedTCA<sup>®</sup>. The timing interface topology is shown in Figure 1-5.

Figure 1-5: AXI timing interface.

## 1.4.2.2.1 CLK100, SYNC, and STRIG Pairs

The CLK100 backplane star distributes a differential 100 MHZ clock from the system slot to the instrument slots. The SYNC star distributes a differential trigger signal from the system slot to the instrument slots. Both the CLK100 and SYNC fabrics have active drivers to fan-out the signals, which are each sourced from the system slot using a single pair. The STRIG star carries bi-directional trigger signals between the system slot and the instrument slots. Each unbuffered Star Trigger signal terminates at the system slot on its own connector pair.

## 1.4.2.2.2 FCLK (PCI Express® Reference Clock Distribution)

AXIe backplanes provide for distribution of a 100 MHz PCI Express<sup>®</sup> reference clock, FCLK, from the system slot to all of the other slots. The FCLK fabric includes active buffers to fan-out the clock as individual, point-to-point differential pairs.

## 1.4.2.3 AXIe Local Bus

The AXIe local bus provides short differential signal pairs between adjacent AXIe slots, excluding the system slot. There are 18 required local bus pairs in each slot-to-slot segment. Backplanes may optionally provide local bus expansion to 42 or 62 pairs.

## 1.4.2.4 Future Zone 3 Extensions

The AXIe architecture is intended to be extensible beyond the needs of general-purpose test and measurement equipment. Future supplemental AXIe specifications (AXIe 3.1, AXIe 3.2, etc.) may add additional features and configurations. These are likely to include the definition of one or more Zone 3 backplane connector configurations.

## 1.4.2.5 Alternate Hub 2 Use

Because AXIe does not require the redundancy features of AdvancedTCA<sup>®</sup>, the Hub 2 (logical slot 2) base and data fabrics are not used to duplicate the functions of the Hub 1 fabrics. AXIe systems do not support AdvancedTCA<sup>®</sup> Hub devices in logical slot 2. Instead, logical slot 2 is defined as an *Instrument Hub* slot. An AXIe instrument hub is an instrument module that may optionally serve as a hub for vendor-defined protocols on the Hub 2 fabric star. Instrument hub slots and modules do not implement the Hub 2 base interface. AXIe instrument hub slots are fully compatible with AXIe instrument modules.

## 1.4.2.6 Additional Electronic Keying

The AXIe architecture requires that devices and systems implement an extended set of electronic keying records to assure the consistent use of AXIe-defined backplane fabrics and resources.

## 1.4.2.7 Additional System Management Requirements

The AXIe architecture requires that each chassis include a dedicated shelf manager.

## 1.4.2.8 Internal EMC Requirements

The AXIe architecture includes EMC requirements for modules and system components that should prevent measurement integrity problems due to electromagnetic interference from components within an AXIe mainframe.

## 1.5 Conformance Requirements

All AXIe products including backplanes, subracks, chassis, and modules, are required to conform to the requirements of this specification. They may also conform to the requirements of the AXIe 2.0 software specification. Some AXIe products may additionally conform to the requirements of other AXIe specifications, such as AXIe 3.1, which sets additional backplane requirements for AXIe products targeted for automated semiconductor test applications.

## 1.6 References

Several other documents and specifications are related to this specification. These include:

- PICMG<sup>®</sup> 3.0 Revision 3.0, AdvancedTCA<sup>®</sup> Base Specification, PCI Industrial Computer Manufacturers Group (PICMG<sup>®</sup>), 401 Edgewater Place, Suite 600, Wakefield, MA 01880 USA, Tel: 781.246.9318, Fax: 781.224.1239, <u>www.picmg.org</u>.

- PICMG<sup>®</sup> 3.4 Revision 1.0, PCI Express<sup>®</sup>/Advanced Switching for AdvancedTCA<sup>®</sup> Systems, PCI Industrial Computer Manufacturers Group (PICMG<sup>®</sup>).

- PCI Express<sup>®</sup> Base Specification, Revision 2.1, PCI-SIG<sup>®</sup>, <u>www.pcisig.com</u>.

- PCI Express<sup>®</sup> Card Electromechanical Specification, Revision 2.0, PCI-SIG<sup>®</sup>.

- VXI-1 Revision 3.0, VMEbus Extensions for Instrumentation System Specification, VXIbus Consortium, <u>www.vxibus.org</u>.

- PXI-5 Revision 1.0, PXI Express Hardware Specification, PXI System Alliance, <u>www.pxisa.org</u>.

- LXI Standard Revision 1.3, LAN Extensions for Instrumentation, LXI Consortium, <u>www.lxistandard.org</u>.

## 1.7 Terminology

AXIe terminology is modeled largely on language familiar to manufacturers, system integrators, and end users in the test and measurement industry. In many cases this is different from the telecom-derived terminology used in the AdvancedTCA<sup>®</sup> specification.

## 1.7.1 AXIe Terms

Here are the definitions of some of the more common AXIe terms:

AXIe Consortium

- **Chassis** This is the primary AXIe infrastructure component that hosts AXIe modules. A typical AXIe chassis includes a backplane, subrack, power supply(ies), fan tray(s), shelf manager, and sheet metal enclosure. It may include rack mounting provisions. A chassis may also include an *embedded system module*. (See *Integrated Chassis.*)

- *Integrated Chassis* An AXIe chassis that has built-in system module functionality in lieu of an AXIe-standard system slot.

- *Module* A PC assembly, face plate, and enclosure that plugs into an AXIe slot. Equivalent to an AdvancedTCA<sup>®</sup> *front board*.

- *System Module* An AXIe module that includes LAN switches, PCIe<sup>®</sup> switches, system timing and trigger resources, and/or other central resources. A system module installs in a chassis system slot. An AXIe system module is comparable to an AdvancedTCA<sup>®</sup> *hub board*.

- Embedded System Module System module functionality that is embedded in an integrated chassis.

- *System Slot* An AXIe slot that supports a *system module*. It is always *logical slot 1*. It is comparable to an AdvancedTCA<sup>®</sup> *hub slot*.

- Instrument Module Any AXIe module that is not a system module.