# **AXIe-2: Base Software Specification**

Revision 2.2 Including provisional changes for revision 2 of AXIe-1

September 13, 2018

# **Important Information**

#### Notice

AXIe-2: Base Software Specification is authored by the AXIe Consortium companies. For a vendor membership roster list, please contact <u>execdir@axiestandard.org</u>.

The AXIe Consortium wants to receive your comments on this specification. To provide such feedback, or to join the consortium, contact <u>execdir@axiestandard.org</u>.

#### Warranty

The AXIe Consortium and its member companies make no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Its member companies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### Trademarks

PICMG, CompactPCI, and AdvancedTCA<sup>®</sup> are registered trademarks of the PCI Industrial Computers Manufacturers Group.

PCI-SIG, PCI Express, and PCIe are registered trademarks of PCI-SIG.

LXI is a trademark of the LXI Consortium Inc.

PXI is a trademark of the PXI Systems Alliance.

IVI is a trademark of the IVI Consortium

VXIplug&play is a trademark of the IVI Consortium

VISA is a trademark of the IVI Consortium

Other product and company names listed are trademarks or trade names of their respective companies.

No investigation has been made of common-law trademark rights in any work.

# Table of Contents

| 1 | Introduction                                                               |    |

|---|----------------------------------------------------------------------------|----|

|   | 1.2 Overview of the AXIe-2: Base Software Specification                    | 7  |

|   | 1.3 Objectives                                                             | 7  |

|   | 1.4 Audience                                                               | 7  |

|   | 1.5 References                                                             | 7  |

|   | 1.6 Definitions of Terms and Acronyms                                      |    |

|   | 1.7 Organization                                                           | 9  |

|   | 1.8 Provisional Changes for Provisional Revision P2.0 of AXIe-2            | 10 |

|   | 1.9 Extensions to the AXIe-2: Base Software Specification                  | 10 |

|   | 1.10 Use of the PXI Software Specifications                                | 10 |

|   | 1.11 Use of the LXI Software Specification                                 | 10 |

|   | 1.12 Use of AdvancedTCA <sup>®</sup> Software Specifications               | 11 |

|   | 1.13 VISA Specification                                                    | 11 |

| 2 | AXIe Software Architecture Overview<br>2.1 AXIe System Software Components |    |

| 3 | Multi-Slot, Multi-Link and Multi-Endpoint Modules                          |    |

|   | 3.2 Multi-Endpoint Modules                                                 |    |

|   | 3.3 Multi-Link Modules                                                     | 15 |

| 4 | Linux Support                                                              | 16 |

| 5 | AXIe Module Software Requirements                                          |    |

|   |                                                                            |    |

| 5.2.1 Slot Number of the AXIe System Module    |  |

|------------------------------------------------|--|

| 5.3 Representing AXIe Triggers                 |  |

| 5.4 System Module Software Requirements        |  |

| 5.4.1 Addressing the System Module and Chassis |  |

| 5.4.2 Reporting Link Information               |  |

| 5.4.3 Reporting the Compact PCI EEPROM         |  |

| 5.4.4 Behavior of the SMBusOperation Function  |  |

| 5.5 Chassis Software Requirements              |  |

| 5.5.1 An Example Chassis Description File      |  |

| 5.6 Peripheral Module Requirements             |  |

|                                                |  |

| 6 | Additional AXIe Software Requirements     |  |

|---|-------------------------------------------|--|

| - | 6.1 Instrument Driver Requirement         |  |

|   | 6.2 Additional AXIe Software Requirements |  |

|   | 6.2.1 GetVersion                          |  |

|   | 6.2.2 GetLUNCount                         |  |

|   | 6.2.3 GetComponentCount                   |  |

|   | 6.2.4 GetFieldCount                       |  |

|   | 6.2.5 GetFieldInfo                        |  |

|   | 6.2.6 GetLinkOrigins                      |  |

|   | 6.2.7 GetLinkWidths                       |  |

|   | 6.2.8 Data types                          |  |

| Α. | Sum   | nmary of the PXI Software Architecture                        | 34 |

|----|-------|---------------------------------------------------------------|----|

|    | A.1   | Overview of PXI System Enumeration                            |    |

|    | A.2   | System enumeration by the Resource Manager                    |    |

|    | A.3   | The PXI Services Tree                                         |    |

|    | A.4   | The PXI System Module driver                                  |    |

|    | A.5   | The PXI Express Peripheral Module driver                      | 39 |

|    | A.6   | Implementation of the Peripheral Module Driver                |    |

|    | A.6.1 | Peripheral Module Driver Behavior for Multi-Slot Modules      |    |

|    | A.6.2 | Peripheral Module Driver Algorithm for Multi-Endpoint Modules |    |

|    | A.6.3 | Peripheral Module Driver Algorithm for Multi-Link Modules     |    |

|    | A.7   | The Chassis Description File                                  |    |

|    | A.8   | Details of the PXI Chassis driver                             | 43 |

|    | A.9   | Peripheral Module Description Files                           | 43 |

|    | A.10  | VISA PXI Plug-in Specification                                |    |

# **Revision History**

This section is an overview of the revision history of the AXIe-2.0 software specification.

| Table 1-1. Software Specification Revisions |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <b>Revision Number</b>                      | Date of Revision  | Revision Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 1.0                                         | November 21, 2011 | Initial revision of the spec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 1.0                                         | January 6, 2012   | Clarified how the system module should respond to mimic a Compact PCI system module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 2.0                                         | March, 2016       | <ul> <li>Various changes: <ul> <li>Updates to reflect that slot 2 is no longer a hub slot.</li> <li>Updates to reflect 4 4-lane links to each peripheral slot</li> <li>Deleted FRUIndex in GetFieldCount in section 4.2.4(6.2.4 per 2.2 changes)</li> <li>Clarified Rule 3.1 to specify requirements with respect to AXIe 1.0 Rev 3.</li> <li>Updated references to the AXIe specifications to the new format. E.g., AXIe-1 instead of AXIe 1.0.</li> <li>Updated 1.9 and 1.12 to reflect updates to IVI and PXI standards.</li> </ul> </li> <li>Provisional Changes: <ul> <li>Added rule 3.13 in section 3.4.3 regarding how to report system slot link width.(5.13 per 2.2 changes)</li> <li>Modified Rule 4.2 in section 4.2 to require AXIe extensions intead of them being optional. (6.2 per 2.2 changes)</li> <li>Provisional additions in 4.2.6 and 4.2.7 to support reporting AXIe 1.0 Rev 3 fabric information(6.2.6 and 6.2.7 per 2.2 changes)</li> </ul> </li> </ul> |  |  |

| 2.1                                         | January 11, 2018  | Added section 1.1 to clarify compliance requirements.<br>and clarified revision as 2.1, which includes<br>provisional changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 2.2                                         | August 1, 2018    | <ul><li>Updates to align with reent PXI revisions. These add:</li><li>Support for Linux operating systems</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                             |                   | • Support for modules that occupy multiple slots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

Table 1-1. Software Specification Revisions

| • Support for modules that have multiple endpoints in the same or different slots.                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Updated section 1.8 to permit devices to cite compliance to this version of the spec and permitting additional compliance statements if they also implement the provisional changes. |

# Table 1-1. Software Specification Revisions

# 1 Introduction

# 1.1 AXIe Compliance

This specification is for use with other AXIe specifications. The AXIe consortium places limitations on the use of the AXIe trademark and requires compliance with certain companion standards. Detailed compliance requirements and trademark usage requirements are in the AXIe Compliance Requirements and Trademark Usage document.

# 1.2 Overview of the AXIe-2: Base Software Specification

AXIe-2 defines software specifications that support the AXIe 1.0 Base Architecture. Both architectures define an extensible platform for general purpose, modular instrumentation. The architecture incorporates the best features of earlier modular open instrumentation platforms, including VXI, PXI, and LXI. Like VXI and PXI, the architecture is based on a popular modular computing platform with added features important to developers and users of test and measurement systems.

The base platform is AdvancedTCA<sup>®</sup>, an open architecture for modular computing components targeted for communications infrastructure applications. The AdvancedTCA<sup>®</sup> architecture includes provisions for power distribution, power and system management, Ethernet communication between modules, and PCI Express communication between modules, along with other capabilities.

The AXIe 1.0 Base Architecture includes some modifications to the AdvancedTCA<sup>®</sup> architecture. These modifications provide timing, triggering, and module-to-module data movement features that are important to the implementation of high-performance test and measurement systems. These modifications are designed to allow most AdvancedTCA<sup>®</sup> computing modules to work within an AXIe 1.0 environment, to allow many general-purpose AXIe devices to work in AdvancedTCA<sup>®</sup> environments, and to prevent any damaging incompatibilities between AXIe and AdvancedTCA<sup>®</sup> devices and system components.

# 1.3 Objectives

The AXIe-2 Base Software Specification specifies the software necessary to support AXIe chassis, system modules, and instrument modules that comply with AXIe-1 Base Hardware Architecture Specification.

The AXIe-2: Base Software Specification builds on the PXI software specifications in much the same way that the AXIe-1: Base Hardware Specification builds on the AdvancedTCA<sup>®</sup> specifications. Specifically, AXIe software is required to substantially comply with PXI-2, *the PXI Software Specification* and PXI-6, the *PXI Express Software Specification*. This permits AXIe system software to be supported by existing PXI utilities; it also facilitates integrating systems composed of both PXI and AXIe components.

# 1.4 Audience

This specification is intended to be used by:

- Product developers interested in implementing and utilizing software features of the AXIe platform.

- Hardware designers interested in referencing description files that identify and describe AXIe hardware capabilities.

- Software designers interested in utilizing descriptors for managing AXIe resources, such as AXIe triggers, local busses, and geographic parameters for slot and chassis identification.

# 1.5 References

Several other documents and specification are related to this specification. These other related documents are the following:

VPP-4.3 Defines the semantics of the VISA library (see <u>www.ivifoundation.org</u>)

www.axiestandard.org

- VPP-4.3.2 VISA Implementation Specification for Textual Languages (see: <u>www.ivifoundation.org</u>)

- **IVI-6.3** VISA PXI Plug-in Specification (see: <u>www.ivifoundation.org</u>)

- **PXI-2** PXI Software Specification (see: <u>www.pxisa.org</u>). References to PXI-2 in this document are to PXI-2 Revision 2.5, May 31, 2018.

- **PXI-4** PXI Module Description File Specification (see: <u>www.pxisa.org</u>). References to PXI-4 in this document are to PXI-4 Revision 1.2, May 31, 2018

- **PXI-6** PXI Express Software Specification (see: <u>www.pxisa.org</u>). References to PXI-6 in this document are to PXI-6 Revision 1.3, May 31, 2018.

- **PXI-8** PXI MultiComputing Software Specification (see: <u>www.pxisa.org</u>). References to PXI-8 in this document are to PXI-8 Revision 1.1, May 31, 2018.

- CompactPCI PICMG 2.0 Specification

#### 1.6 Definitions of Terms and Acronyms

This section defines terms and acronyms used in this specification:

| PXI          | This term originates from PXISA.org and refers broadly to the PXI specifications and compliant components; this includes both PXI Express and PXI-1.                                                                                                                                                                                                                                                         |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PXI-1        | This term originates from PXISA.org and refers specifically to PXI modules that are based on parallel PCI and not PCI Express.                                                                                                                                                                                                                                                                               |

| System       | A system is a collection of one or more chassis. Each chassis may be an AXIe chassis or a PXI chassis.                                                                                                                                                                                                                                                                                                       |

| Chassis      | A chassis is a unit that contains a backplane, a system module, instrument modules, and a shelf manager.                                                                                                                                                                                                                                                                                                     |

| Instrument   | <b>Module</b> This is a card that plugs into an instrument slot within an AXIe chassis. In AdvancedTCA <sup>®</sup> , these cards are loosely referred to as "blades".                                                                                                                                                                                                                                       |

| Peripheral [ | <b>Module</b> This term is synonymous with Instrument Module. It is commonly used in PXI and Compact PCI. This term is generally used in this document to be consistent with the referenced PXI specifications.                                                                                                                                                                                              |

| System Mo    | <b>dule</b> The system module provides the communication interface, both network and PCIe, outside the chassis. The system module also distributes these communication fabrics among the modules.                                                                                                                                                                                                            |

| Shelf Mana   | <b>ger</b> The Shelf Manager Module, also referred to as the <i>ShMM</i> , interacts with modules in the chassis as well as other Field Replaceable Units (FRU), such as power supplies and fans. The shelf manager maintains an inventory of these units and is responsible for powering and monitoring of modules over an independent IPMB backplane bus. Much more information may be found in PICMG 3.0. |

| System Mo    | <b>dule Driver</b> The driver defined by PXI-6 that enumerates system modules and the chassis they connect to and provides API access to the chassis and system modules.                                                                                                                                                                                                                                     |

**Chassis Driver** The driver defined by PXI-6 that returns information about the chassis. In AXIe and PXI Express chassis information is primarily provided by the system module driver, however AXIe-2 defines additional APIs that provide FRU information.

114 1 1 5 1

| Peripheral | peripheral modules.                                                                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPMC       | Intelligent Platform Management Controller. The microcontroller that provides a IPMB connection to the ShMC. Although required, on an instrument module, an IPMC may reside in the chassis and provide other services such as power supply monitoring. |

| ShMC       | Shelf Manager Controller. The microcontroller that resides on the shelf and is the master of the IPMB.                                                                                                                                                 |

| FRU        | Field replaceable unit. This term refers to a set of functionality on an AXIe module. This is a historical term and the referenced functionality may not actually be a replaceable unit.                                                               |

• •

..

1 . •.

# 1.7 Organization

This specification was created and is maintained under the rules of the AXIe consortium.

1.

-

1 C

This specification consists of a system of numbered RULES, RECOMMENDATIONS, PERMISSIONS, and OBSERVATIONS, along with supporting text, tables, and figures.

**RULE**s outline the requirements of the specification. They are characterized by the keyword "**SHALL**". Conformance to these rules provides the necessary level of compatibility to support the multi-vendor interoperability expected by system integrators and end users in the test and measurement industry. Products that conform to this specification must meet all of the requirements spelled out in the various rules.

**RECOMMENDATION**s provide additional guidance that will help AXIe equipment manufacturers improve their users' experiences with AXIe systems. They are characterized by the keyword "**SHOULD**". Following the recommendations should improve the functionality, flexibility, interoperability, and/or usability of AXIe products. Products are not required to implement the recommendations.

**PERMISSION**s explicitly highlight some of the flexibility of the AXIe specification. They are characterized by the keyword "**MAY**". The permissions generally clarify the range of design choices that are available to product and system designers at their discretion. They allow designers to trade off functionality, cost, and other factors in order to produce products that meet their users' expectations. Permissions are neutral and imply no preference as to their implementation.

**OBSERVATION**s explicitly highlight some of the important nuances of the specification. They help the readers to fully understand some of the implications of the specification's requirements and/or the rationale behind particular requirements. They generally provide valuable design guidance.

All rules, recommendations, permissions, and observations must be considered in the context of the surrounding text, tables, and figures. Rules may explicitly or implicitly incorporate information from the text, tables, and figures. Although the authors of this specification have gone to significant effort to insure that all of the necessary requirements are spelled out in the rules, it is possible that some important requirements appear only in the specification's free text. Conservative design practice dictates that such embedded requirements be treated as rules.

The AXIe-2 specification is based on several PXISA<sup>®</sup> specifications and AXIe 1.0 hardware specifications. Relevant PXISA<sup>®</sup> numbered requirements are explicitly referenced in this specification's rules, recommendations, permissions, and observations. These requirements are incorporated along with their supporting context (text, tables, figures, etc.). Any numbered requirement that is not explicitly included by this specification's rules, recommendations, permissions, or observations, is excluded from the AXIe-2 requirements.

Successful implementation of AXIe products and systems requires in-depth knowledge of the AXIe 1.0 Base Architecture Specification and PXISA<sup>®</sup> specifications.

# 1.8 Provisional Changes for Provisional Revision P2.0 of AXIe-2

The initial release of revision 2.0 of this specification was passed provisionally. That is, the AXIe consortium believes the changes made for revision 2.0 to be accurate and complete further the consortium expects them to be required for compliance with the specification. However, subject to implementation and interoperation testing, the changes and additions to the specification may need to be revisited. Once suitably verified, the changes will be either confirmed or, if necessary, extension and corrections consistent with the direction established by the provisional changes may be added.

The provisional changes are:

- Added Rule 5.14 in section 5.4.3 regarding how to report system slot link width.

- Modified Rule 6.2 in section 6.2 to require AXIe extensions intead of them being optional.

- Provisional additions in 6.2.6 and 6.2.7 to support reporting AXIe 1.0 Rev 3 fabric information

Any implementation the complies with all of the non-provisional rules is permitted to cite compliance to AXIe-2, Revision 2.2. Implementations that further comply with the provisional rules listed above are permitted to cite compliance to "AXIe-2 Revision 2.2, provisional changes".

# 1.9 Extensions to the AXIe-2: Base Software Specification

The AXIe modular architecture is intended to be an extensible architecture. An extension may focus on a specific niche market requirement that is not considered advantageous to be a part of the base specification. In contrast the base specification describes attributes and features that are advantageous to be common across all extensions. Such commonality is beneficial across the AXIe community.

An example of a hardware extension might be a specific market application using the Zone 3 interface. Such an extension likely has software features targeted for using that hardware extension. These hardware and software extensions would be described in separate hardware and software specifications specific to the extension. Such extensions must be adopted and approved by the AXIe Consortium Committee.

# 1.10 Use of the PXI Software Specifications

This specification leverages from well known and understood standards such as the PXI specifications. Where possible, the AXIe standard directly uses the PXI software specification. This simplifies implementation, system integration, promotes adoption, and encourages reuse.

In addition, AXIe contains elements that do not exist in PXI but must be supported by the base software. The requirements in this specification regarding those elements do not conflict with any PXI requirements.

No provisions in this specification conflict with, or alter the PXI requirements.

The PXISA has defined a mechanism for software clients to reserve backplane trigger lines. AXIe chassis are encouraged to comply with PXI-9 in order for clients to reserve AXIe trigger lines (note that routing is not meaningful for AXIe chassis).

The PXI-8, *PXI MultiComputing Software Specification* defines shared memory and other standard protocols to allow CPU based device to communicate through non-transparent bridges. Compliance with PXI-8 is optional for AXIe equipment.

# 1.11 Use of the LXI Software Specification

The AXIe software specification recommends that AXIe network modules comply with LXI where practical. Further details of software requirements for the network connection on modules may be incorporated in a latter version of this standard. The shelf manager in an AXIe system has a network interface. In AdvancedTCA<sup>®</sup> systems, the shelf manager is statically configured to a fixed IP address during configuration. AXIe systems are more dynamic in that they may be set up, configured, modified, and moved to suit a particular test configuration. The network fabric in these cases may be part of a DHCP served environment in which IP addresses are subject to change. Chassis and system designers should create their shelf managers to be friendly entities on the network and attain IP addresses using DHCP or Dynamically Configured Link Local Addressing<sup>1</sup>.

# 1.12 Use of AdvancedTCA® Software Specifications

AdvancedTCA<sup>®</sup> provides a rich feature set of hardware and software functionality. The AXIe 1.0 Base Architecture Specification, Chapter 3, *Hardware Platform Management*, summarizes important attributes of AdvancedTCA<sup>®</sup> and how these relate to an AXIe system context. This chapter references several other specifications that describe e-keying functionality, FRU records, the Intelligent Platform Management Interface (IPMI 1.5), and Remote Management Control Protocol (RMCP). These standards permit a common set of software tools to interact with shelf and board management features. There are vendors today that already specialize in promoting shelf managers and board management controllers adhering to these AdvancedTCA<sup>®</sup> recommendations.

# 1.13 VISA Specification

The IVI Foundation defines a family of VXI*plug&play* specifications that include the VISA specifications which define a standard IO library. The basic capabilities of the library are defined in the VPP-4.3 specification, *The VISA Library*. VPP-4.3.2, *VISA Implementation Specification for Textual Languages*, defines how the library is implemented for textual languages.

The IVI suite of VISA standards includes IVI-6.3, *IVI VISA PXI Plug-in* which defines a stand-alone VISA plug-in which may be called by VISA to perform PXI IO for a specific device. Although beyond the scope of this specification, this is a useful mechanism for doing IO to AXIe devices that comply with this specification.

This is especially useful since PXI-2 section 3.6 requires that all system controllers shall provide a VISA implementation that supports the PXI bus and complies with the VISA library specifications, version 4.0 or higher. By using the VISA Plug-In, vendors need not provide a full VISA library.

Information regarding the VISA standards is available from the IVI Foundation.

<sup>&</sup>lt;sup>1</sup> Per RFC 3927, Dynamic Configuration of Ipv4 Link-Local Addresses

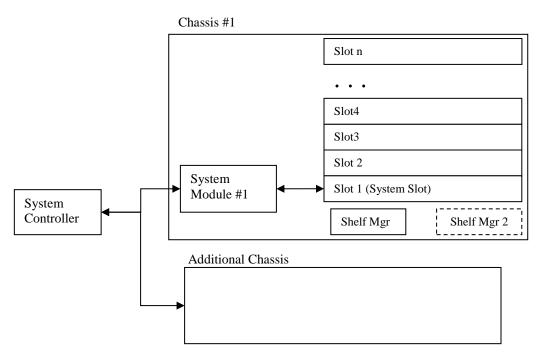

Figure 1 Hardware Components of an AXIe System

An AXIe system's heritage is based upon AdvancedTCA<sup>®</sup>, PICMG 3.0, and PXI. The AXIe architecture adds several extensions beyond the scope of telecommunication applications into test and measurement applications. AXIe provides both network and PCIe interconnect fabrics. Additionally, there are dedicated clocks, synchronization, and triggering signals specifically added for instrumentation. For more details on the hardware architecture, refer to the AXIe 1.0 Base Architecture Specification.

The key components of the system are shown in Figure 1, Hardware Components of an AXIe System. Note that:

- There is a single host computer in the system, called the *system controller*. Multiple system modules may be connected to the system controller. Although the host computer may be embedded in the AXIe chassis, the software architecture remains the same.

- The *system module* (SM) is the hardware that provides the connectivity to the chassis. The system module must occupy the system slot in an AXIe chassis, and provide connectivity to the system controller. There is one system module per chassis.

- AXIe-2 uses the physical slot number to reference slots. Throughout this document, any reference to slots refers to the physical slot unless further qualified. The physical slot is the slot designation that is visible to a user looking at the front of the chassis, and are labelled from left to right or bottom to top per ATCA specifications. Although individual modules and their software may not know the physical address, the chassis can provide that information using ATCA specified protocols.

The physical slot is available to AXIe modules by interrogating the ShMC which maintains a site number lookup list which can be interrogated using standard ATCA netFN (net function) commands over IPMB.

• Each chassis contains a number of slots, including one system slot, an instrument hub slot, and instrument slots (also known as peripheral slots). The system slot is always logical address 1, but not necessarily physical slot 1. Furthermore, a chassis vendor may choose to integrate system module functionality into a chassis. In this case, the system module is referred to as an *embedded system module* and the physical slot

number reported shall be 0. A chassis that has an embedded system module is referred to as an *integrated chassis*.

• The shelf manager is associated with an individual chassis. Although not required as part of AXIe, there may be a redundant shelf manager for the purpose of high availability systems. This backup shelf manager transparently assumes the role of the primary shelf manager in the event of failure.

The AXIe hardware specification permits combining system controllers, system modules, chassis, and instrument modules from different vendors. The basic purpose of the AXIe-2 Base Software Specification is to provide the minimum software infrastructure to permit system providers to assemble systems from different components without tying the software to a specific vendor's implementation.

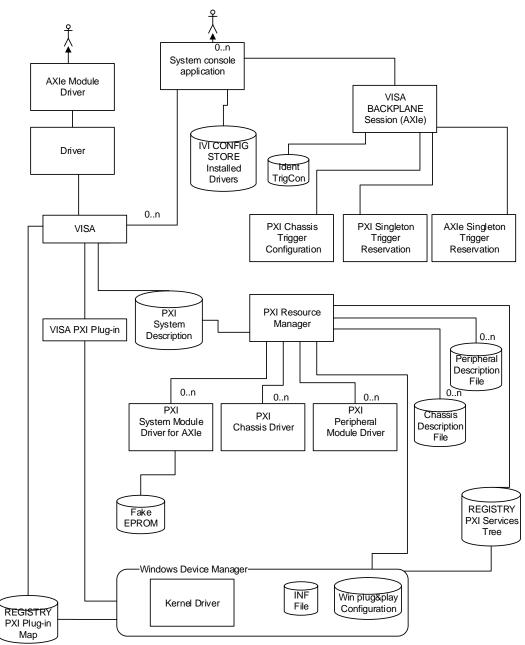

# 2.1 AXIe System Software Components

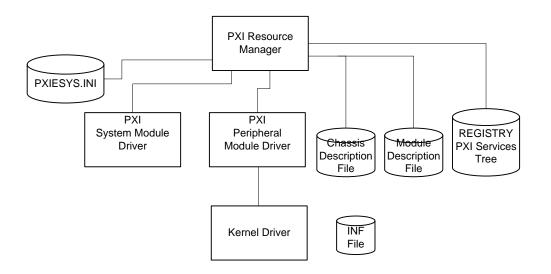

#### Figure 2 Basic AXIe system discovery showing the PXI modules used.

Figure 2 shows the PXI components that are involved in the discovery and enumeration of an AXIe system. The requirements regarding this software are the purview of the PXI specifications. An overview of their operation and how they work with AXIe is in Appendix A.

Details of this enumeration process are specified PXI-2 and PXI-6.

PXI-4 describes an optional module description file. This file contains information about the specific module. The resource manager may incorporate this information in the system description file (that is, the PXIESYS.INI file). In this case, The information from the module description file is embedded within the descriptor for the slot that contains this module in the system description file. For instance, if a module *foo* has a module description file with an entry *bar* = *"baz"*. For each slot that contains the foo module, the PXIESYS.INI file will include the descriptor line *bar*=*"baz"*.

The module description file is optional for both PXI and AXIe devices.

The INF File shown in the illustration is provided along with the module kernel driver in order for the Windows operating system to correctly identify and install the kernel driver. Linux installations do not have this mechanism.

See Appendix A, Summary of the PXI Software Architecture, for additional detail on the PXI software architecture.

# 3 Multi-Slot, Multi-Link and Multi-Endpoint Modules

| 1 Slot Module - 1 end pont   |      |  |  |  |

|------------------------------|------|--|--|--|

| Α                            | 7    |  |  |  |

| 1 Slot Module - 2 end points |      |  |  |  |

| В                            | 9 10 |  |  |  |

| 3 Slot Module - 1 end point  |      |  |  |  |

| 3 : | Slot | Mo | dul | e - | 2 | end | points |

|-----|------|----|-----|-----|---|-----|--------|

|-----|------|----|-----|-----|---|-----|--------|

| D | 12 |

|---|----|

|   |    |

|   | 14 |

3 Slot Module - 2 end points in first slot and 1 end point in other slots

| Е | 19    |

|---|-------|

|   | 18    |

|   | 16 17 |

#### Figure 3 Examples of Multi-Slot, Multi-Link and Multi-Endpoint Modules

This topic describes the discovery mechanisms specified by PXI for:

• Modules that occupy multiple slots

11

• Modules that place multiple endpoints in a single slot

## 3.1 Multi-Slot Modules

С

Multi-Slot Modules occupy more than one slot. In Figure 3, C, D and E are Multi-Slot Modules. Effective with the PXI standard updates in 2018, the peripheral module driver supports calls that return:

- Slot Number Slot number where the link is currently connected

- Occupied slot count Number of slots occupied by this device

- Slot number offset Number of chassis slots the module occupies that are to the left of the slot reported. For example, zero indicates that the occupied slot is the leftmost slot, and the module extends to the right by the occupied slot count minus 1.

# 3.2 Multi-Endpoint Modules

In Figure 3, B is an example of a multi-endpoint module. It contains a switch and two endpoints. Note that the operating system instantiates a kernel driver for each endpoint and each represents a PCI Express link. (Note, in PCI, the term link refers to a PCI connection between two devices).

PXI specifies that the API used to query links only report a single link for this slot, even though there are PCI Express links to both bus 9 and bus 10. PXI recommends that the connection to the backplane (from the switch) be reported from the module, but this is frequently not practical because there is not a generic way to determine the path to the switch on some operating systems. Therefore, peripheral module drivers are permitted to onlyreport the links to the endpoints.

To report two endpoints, the peripheral module driver returns the address of both endpoints in the address\_info query as a semicolon separated string:

• For a single endpoint device, the address\_info returns a VISA bus, device, function address string. For example: "PXI0::9-0.0::INSTR" (not including the quotes)

• For a multiple endpoint module, the peripheral module driver returns the VISA address for each endpoint, separated by commas. For example: "PXI0::9-0.0::INSTR;PXI0::10-0.0::INSTR" (not including the quotes) indicates two endpoints with bus addresses 9 and 10.

For instance, the first identified end-point address may be the main FPGA, the second endpoint could be for inbound streaming, and the third for out-bound streaming. Thus, the instrument driver can access this string to determine how the module was enumerated.

The PXI standard does not specify the significance of the order of the addresses in the address\_info string. However, the IVI VISA standard specifies that VISA sessions can be opened to each endpoint by specifying the index of the endpoint in the string. This is important because neither the PCI specification nor the operating system guarantee the order in which the PCI bus numbers are assigned for each endpoint on the module.

This same technique is used when a multi-endpoint module within a multi-slot module is reported.

# 3.3 Multi-Link Modules

The PXI Express standard refers to modules that occupy multiple slots where endpoints are connected to the backplane from more than one slot as multi-link modules. This is somewhat of a misnomer in that a multi-endpoint module also has multiple PCI links. These links all appear to be part of a single multi-slot module to the end user. In Figure 3, D and E are Multi-Link Modules.

For these modules, PXI specifies that a peripheral module driver reports the presence of a link in each slot that contains a link to the backplane. Therefore, the module reports both links, each describing the location and full width of the module and the offset of this link within the module. Thus, it is apparent to the resource manager that the module is three slots wide, and that there are links to the first and third slots because the installed peripheral module drivers report overlapping geographical locations for the modules.

# 4 Linux Support

PXI specifies Linux and Windows frameworks for both 32 and 64-bit operating systems. The architecture of the two is substantially the same, and thus the operating system has very little impact on the standard itself. The most notable difference is that the registration and configuration information on Windows is stored in the Windows 32-bit registry. On Linux, configuration information is stored in the file system.

AXIe-2 permits AXIe components to support any of the PXI-defined frameworks, including Linux, Windows, or both. Products should provide clear documentation of the supported framework.

In the case of Windows, the Windows registry provides a hierarchical organization for the installation data, and all installation data is stored in the 32-bit registry in a registry hive specified by the PXI standards alliance. Since Linux does not have an intrinsic data storage mechanism the configuration information is stored in a specified location on the Linux file system in INI files. The Linux file system hierarchy replicates the registry hierarchy on Windows.

PXI-2 specifies the location where the registration data is placed on the file system, and how the INI files are formatted and organized within the file system to provide the registration information required by PXI and AXIe. The PXI-2 specification also specifies the details of the group and user ownership of the created files.

INI files themselves do not have a tightly specified syntax, therefore the PXI standard specifies the syntax used in the INI files. This is a simple and conventional INI format and is the same format that is used for other INI files used in both the Windows and Linux frameworks. For instance the PXIESYS.INI file and the chassis INI file use the same syntax.

- **RULE 4.1:** AXIe devices that support Linux shall comply with one or both of the Linux frameworks as specified by PXI in PXI-2 and PXI-6

- **RULE 4.2:** AXIe devices that support Windows shall comply with one or both of the Windows frameworks as specified by PXI in PXI-2 and PXI-6.

# **5 AXIe Module Software Requirements**

In order to facilitate the development and deployment of AXIe systems alongside PXI systems, the AXIe software requirements are based on the PXI software requirements.

**RULE 5.1:** AXIe chassis providers, system module providers, and instrument module providers are required to provide software components as required by the PXI standards for PXI Express devices. The relevant PXI standards for these devices are PXI-2, *PXI Software Specification*, and PXI-6, *The PXI Express Software Specification*.

In addition, AXIe providers are required to provide software that complies with all other rules in this specification. AXIe hardware that complies with earlier versions of AXIe-1 than 3.0 shall comply with AXIe-2 revision 1.0. AXIe hardware that complies with AXIe-1 version 3.0 shall comply with AXIe-2 revision 2.0 or later.

Since there are certain intrinsic differences between PXI and AXIe, a small number of differences exist between the AXIe deliverables and PXI deliverables. In some cases, the differences are only in the implementation, in other cases, the PXI deliverable may not be relevant for AXIe.

Further, since AXIe provides capabilities beyond the scope of PXI, these are described separately in a way that permits compatibly deploying AXIe and PXI, and also provides the necessary incremental information for AXIe peripherals.

# 5.1 PXI Compliance Requirements for AXIe Components

**RULE 5.2:** AXIE System Modules, Chassis, and Peripheral modules shall comply with the corresponding requirements in PXI-6, Revision 1.3, subject to the explanations and caveats in Table 2, *Details of how PXI-6 bears on AXIe components*.

Note that PXI requires that the system controller provide a resource manager. Table 2, *Details of how PXI-6 bears on AXIe components* includes a column highlighting the PXI requirements for the resource manager. A PXI compliant resource manager will correctly enumerate an AXIe system and create a correct PXIESYS.INI file that includes the AXIe system.

In Table 2, Details of how PXI-6 bears on AXIe components:

- Req Indicates that this requirement shall be satisfied by the module in the corresponding columnNA Indicates that this requirement is not applicable to the module in the corresponding column

- *<other>* Other text in this field indicates the required behavior for the module in the corresponding column

| PXI-6 Section                | System<br>Controller<br>(Resource<br>Manager) | System Module | Shelf/Chassis | Peripheral<br>Module |

|------------------------------|-----------------------------------------------|---------------|---------------|----------------------|

| 2.1 Common File Requirements | NA                                            | Req           | Req           | Req                  |

| 2.1.1 Version Descriptor     | NA                                            | Req           | NA            | NA                   |

#### Table 2 Details of how PXI-6 bears on AXIe components

17 Copyright © 2011-2018 AXIe Consortium. All rights reserved.

| PXI-6 Section                                 | System<br>Controller<br>(Resource<br>Manager) | System Module | Shelf/Chassis               | Peripheral<br>Module |

|-----------------------------------------------|-----------------------------------------------|---------------|-----------------------------|----------------------|

| 2.2.1 System Description<br>Definitions       | Req                                           | NA            | NA                          | NA                   |

| 2.2.2 Resource Manager<br>Descriptor          | Req                                           | NA            | NA                          | NA                   |

| 2.2.3 System Descriptor                       | Req                                           | NA            | NA                          | NA                   |

| 2.2.4 Chassis Descriptor                      | Req                                           | NA            | NA                          | NA                   |

| 2.2.5 Trigger Bus Descriptor                  | Req                                           | NA            | NA                          | NA                   |

| 2.2.6 Trigger Bridge Descriptor               | Req                                           | NA            | NA                          | NA                   |

| 2.2.7 Line Mapping Specification Descriptor   | Reg                                           | NA            | NA                          | NA                   |

| 2.2.8 Star System Timing Sets Descriptor      | Req                                           | NA            | NA                          | NA                   |

| 2.2.9 Star Trigger Descriptor                 | Req                                           | NA            | NA                          | NA                   |

| 2.2.10.1 System Slot Descriptors              | Req                                           | NA            | NA                          | NA                   |

| 2.2.10.2 Peripheral Slot Descriptor           | Req                                           | NA            | NA                          | NA                   |

| 2.2.11.1 Single-Chassis PXI<br>Express System | Req                                           | NA            | NA                          | NA                   |

| 2.3 Chassis Description Files                 | NA                                            | NA            | Req                         | NA                   |

| 2.3.2 Chassis Descriptor                      | NA                                            | NA            | Req                         | NA                   |

| 2.3.3 Trigger Bus Descriptor                  | NA                                            | NA            | Req                         | NA                   |

|                                               |                                               |               | AXIe has a fixed single bus |                      |

| PXI-6 Section                               | System<br>Controller<br>(Resource<br>Manager) | System Module | Shelf/Chassis                                                                                                                               | Peripheral<br>Module |

|---------------------------------------------|-----------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2.3.4 Trigger Bridge Descriptor             | NA                                            | NA            | Req                                                                                                                                         | NA                   |

| 2.3.5 Line Mapping Specification Descriptor | NA                                            | NA            | Req                                                                                                                                         | NA                   |

| 2.3.6 Star System Timing Sets<br>Descriptor | NA                                            | NA            | Required as described in section 5.3                                                                                                        | NA                   |

| 2.3.7 Star Trigger Descriptor               | NA                                            | NA            | Required as described in section 5.3                                                                                                        | NA                   |

| 2.3.8 PXI-1 Bus Segment<br>Descriptor       | NA                                            | NA            | AXIe chassis<br>shall NOT<br>include a PXI-1<br>bus segment<br>descriptor unless<br>they have<br>special<br>provisions for<br>PXI-1 devices | NA                   |

| 2.3.9 Slot Descriptor                       | NA                                            | NA            | Req                                                                                                                                         | NA                   |

| 3.3.1 System Module Drivers                 | NA                                            | Req           | NA                                                                                                                                          | NA                   |

| 3.3.2 Chassis Drivers                       | NA                                            | NA            | Not required<br>since AXIe<br>devices are PCIe<br>and this<br>component is a<br>PXI-1<br>requirement.                                       | NA                   |

| 3.3.3 Peripheral Module Drivers             | NA                                            | NA            | NA                                                                                                                                          | Req                  |

| 3.3.4 Status Codes                          | NA                                            | Req           | Req                                                                                                                                         | Req                  |

| 3.4 Registration of Services                | NA                                            | Req           | Req                                                                                                                                         | Req                  |

| 3.4.1 Services Tree                         | NA                                            | Req           | Req                                                                                                                                         | Req                  |

| 3.5 System Enumeration                      | NA                                            | Req           | NA                                                                                                                                          | NA                   |

19 Copyright © 2011-2018 AXIe Consortium. All rights reserved.

| PXI-6 Section                                                                                        | System<br>Controller<br>(Resource<br>Manager) | System Module | Shelf/Chassis | Peripheral<br>Module |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------|---------------|----------------------|

| 3.5.1 Resource Manager Algorithm                                                                     | Req                                           | NA            | NA            | NA                   |

| 3.5.2 Determining Chassis<br>Numbers                                                                 | Req                                           | NA            | NA            | NA                   |

| 3.5.3 Handling Driver Errors                                                                         | NA                                            | Req           | NA            | NA                   |

| <b>4.2 PXI Software Compatibility</b><br>(this section requires compliance<br>with PXI-2, section 3) | NA                                            | Req           | Req           | Req                  |

| 4.3 32-bit Windows System Framewo                                                                    | rk                                            |               |               |                      |

| 4.3.2 System Description File Location                                                               | NA                                            | Req           | NA            | NA                   |

| 4.3.3 System Configuration File Location                                                             | NA                                            | Req           | Req           | NA                   |

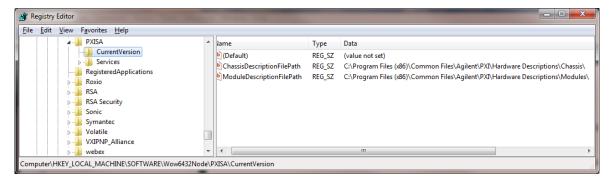

| 4.3.4 Chassis Description File Path Location                                                         | NA                                            | Req           | Req           | NA                   |

| 4.3.5 Driver Software Bindings                                                                       | NA                                            | Req           | Req           | Req                  |

| 4.3.6 Services Tree Implementation                                                                   | NA                                            | Req           | Req           | Req                  |

| 4.4 64-bit Windows System Framewo                                                                    | ork                                           |               |               |                      |

| 4.4.2 System Description File Location                                                               | NA                                            | Req           | NA            | NA                   |

| 4.4.3 System Configuration File Location                                                             | NA                                            | Req           | Req           | NA                   |

| 4.4.4 Chassis Description File Path Location                                                         | NA                                            | Req           | Req           | NA                   |

| 4.4.5 Driver Software Bindings                                                                       | NA                                            | Req           | Req           | Req                  |

| 4.4.6 Services Tree Implementation                                                                   | NA                                            | Req           | Req           | Req                  |

| 4.5 32-bit Linux System Framework                                                                    |                                               |               |               |                      |

| PXI-6 Section                                                   | System<br>Controller<br>(Resource<br>Manager) | System Module | Shelf/Chassis | Peripheral<br>Module |

|-----------------------------------------------------------------|-----------------------------------------------|---------------|---------------|----------------------|

| 4.5.2 System Description File Location                          | NA                                            | Req           | NA            | NA                   |

| 4.5.3 System Configuration File Location                        | NA                                            | Req           | Req           | NA                   |

| 4.5.4 Chassis Description File Path Location                    | NA                                            | Req           | Req           | NA                   |

| 4.5.6 Services Tree Implementation                              | NA                                            | Req           | Req           | Req                  |

| 4.5.7 Security of PXI Files and Interfaces                      | NA                                            | Req           | Req           | Req                  |

| 4.6 64-Bit Linux System Framework                               |                                               |               |               |                      |

| 4.6.2 System Description File Location                          | NA                                            | Req           | NA            | NA                   |

| 4.6.3 System Configuration File Location                        | NA                                            | Req           | Req           | NA                   |

| 4.6.4 Chassis Description File Location                         | NA                                            | Req           | Req           | NA                   |

| 4.6.5 Driver Software Bindings                                  | NA                                            | Req           | Req           | Req                  |

| 4.6.6 Services Tree Implementation                              | NA                                            | Req           | Req           | Req                  |

| 4.6.7 Security of PXI Files and Interfaces                      | NA                                            | Req           | Req           | Req                  |

| Appendix: 32-Bit Windows System<br>Framework Files <sup>2</sup> | NA                                            | Req           | Req           | Req                  |

# 5.2 AXIe Slot Numbers, Physical Addresses, and Logical Addresses

All AXIe devices have multiple addresses including:

www.axiestandard.org

- **Physical Address** This identifies the physical location of the module within the frame. AdvancedTCA® requires that the leftmost (or bottom) slot be 1 and increment from left to right (or bottom to top).

- Logical Address A Slot within a Shelf defined by the Zone 1 Hardware Address. Every Slot has a unique Logical Slot number (maximum of 16 Logical Slots per Shelf). Logical Slot numbers are used to determine Channel mapping between Slots. PICMG® 3.0 defines a direct correlation between Channel numbers and Logical Slot numbers. For example, Channel 1 (Base and/or Fabric Channels) of every Slot establishes a direct connection to Logical Slot 1.

- Hardware Address This address is set by using 7 lines directly connected to each module. This corresponds to the PXI geographical address. This same address is used as the IPMB address. The hardware address and physical address in AXIe differ numerically by 0x40 (64 decimal) (per AdvancedTCA<sup>®</sup> section 3.2.3.2).

For the purposes of this spec and relating AXIe to PXI, the slot number reported as the PXI slot number shall be the AXIe *physical address*.

**RULE 5.3:** When an AXIe peripheral module driver reports the module's slot number, it shall report the AXIe physical address.

#### 5.2.1 Slot Number of the AXIe System Module

- **RULE 5.4:** If the system module is not an embedded system module, it shall use its physical address as the PXI slot where the system module is located.

- **RULE 5.5:** If the system module is an embedded system module, that is, the system module is embedded in the chassis, then the system module shall use a PXI slot of 0.

The address of the system slot appears in the system description file. It is available to the resource manager via the CompactPCI EPROM information.

Furthermore, since the AXIe System Slot provides timing functionality, the system slot should be reported as the timing module slot.

System software designed for PXI, where the system module is always at slot number 1, may have to be extended to properly support AXIe slot system module slot numbers which may be any slot, or zero in the case of an embedded system module.

#### 5.3 Representing AXIe Triggers

RULE 5.6: AXIe description files shall use the system slot number as the PXI timing slot.

Table 3, *AXIe trigger representation in the PXI chassis description file*, describes how AXIe triggers shall be described to the PXI system software.

| Context                                                                                                                  | PXI<br>definition<br>and usage                                                                                                                                                                                                                                               | AXIe      |                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger Bus<br>Descriptor                                                                                                | Describes<br>the<br>electrically<br>separate<br>PXI trigger<br>buses. Note<br>that external<br>control<br>handles<br>buffering<br>between<br>segments.                                                                                                                       | Slc<br>   | AXIe chassis TriggerBus<br>descriptor shall always indicate a<br>single non-segmented trigger bus<br>to each slot.<br>siggerBus1]<br>otList = 1,2,3,4,5,6,<br>otList includes all slots in the<br>ding the system module slot. |

| Star System Timing<br>Sets Descriptor (that<br>is the connections of<br>the star triggers<br>defined for PXI<br>Express) | A single<br>timing set<br>descriptor is<br>included for<br>each timing<br>slot in the<br>chassis.<br>Each<br>indicates the<br>mapping of<br>the set of 3<br>PXI Express<br>DTAR<br>triggers<br>between<br>timing slot<br>outputs and<br>module<br>DSTAR<br>trigger<br>inputs | RULE 5.8: | The AXIe chassis shall not<br>include a StarSystemTimingSet<br>descriptor since the single AXIe<br>star trigger is reported with a<br>StarTriggerDescriptor.                                                                   |

Table 3 AXIe trigger representation in the PXI chassis description file

| Context                                                                                            | PXI<br>definition<br>and usage                                                                                                                                                                                                         | AXIe                                               |                                                                                                                               |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Star Trigger<br>Descriptor (that is,<br>the connection of<br>the star trigger<br>defined by PXI-1) | For each<br>slot, a<br>description<br>of which<br>timing slot<br>trigger<br>output is<br>routed to<br>which<br>module slot.<br>Note that<br>the PXI-1<br>star trigger<br>is a single<br>bidirectional<br>trigger<br>much like<br>AXIe. | Sys<br>PXI<br>PXI<br>The system t<br>containing th | descriptor always indicates a<br>single star trigger to each slot,<br>with the system module slot as<br>the SystemTimingSlot. |

#### 5.4 System Module Software Requirements

The following sections describe software requirements regarding the system module.

#### 5.4.1 Addressing the System Module and Chassis

- **RULE 5.10:** The *address\_info* value returned by the system module driver *PXISA\_SystemModule\_GetName* function shall return a string that a client can use to open a session to either a chassis or system module software programming interface (that is, an *instrument driver*) to both chassis and system module functions.

- **RULE 5.11:** The *address\_info* string is constructed by concatenating the VISA address of the chassis with the "+" character and the VISA address of the system module. In the case of an embedded system module, if the drivers for both the system module and the shelf may be opened using the same string, a single VISA address string may be used.

For instance, if an IVI driver is provided to control the chassis, the *address\_info* string can be passed to the *Initialize* function to open a session to this particular chassis. Similarly, the same string can be passed to the *Initialize* function of the IVI driver for the system module to open a session with this system module.

For example, if the IP address of the chassis were 192.168.1.0 and the IP address of the system module were 192.168.1.1, an appropriate addressInfo response would be:

TCPIP::192.168.1.0::SOCKET+TCPIP::192.168.1.1:SOCKET

Note that the resource manager will place this string in the PXIESYS.INI file where it can be accessed by client software. Further, spaces are not allowed in the the *address\_info* string.

#### 5.4.2 Reporting Link Information

PXI systems may provide either 2 or 4 links to the system controller, each of varying width. These may be directly connected to a limited number of modules, or routed through PCI switches for more flexible connections. AXIe

system modules have a star topology, with 1 to 4 PCI Express connection to each slot. In order to interoperate with PXI systems and PXI system software, AXIe modules report artificial values.

The AXIe system module driver shall report 2 8-lane connections and associate at least one actual bus number and subordinate bus number with each reported link in order to respond to the various queries issued with the *PXISA\_SystemModule\_GetInformation* call.

**RULE 5.12:** The system module driver *PXISA\_SystemModule\_GetInformation* call shall indicate 2, 8-lane links. The bus number range reported for these two links shall both be non-empty. All of the bus numbers of the links to the instrument modules shall be associated with one and only one of the two links.

# 5.4.3 Reporting the Compact PCI EEPROM

- **RULE 5.13:** System Modules that only implement AXIe-1 versions before Rev 3 shall provide a system module driver. The *PXISA\_SystemModule\_GetChassisEeprom* shall return a data structure constructed to mimic a Compact PCI EEPROM. Specifically, the following fields shall reflect the corresponding AXIe chassis information:

- Vendor ID (string)

- Model (string)

- Serial Number (string)

- Slot Count (byte)

- Peripheral Slot Count (physical number of peripheral slots)

- System Slot number, that is, the physical address of the system slot (byte)

- System Slot type (AXIe shall always report a 2-Link slot type)

- System Slot Link 1 width (AXIe shall always report an 8-lane link)

- System Slot Link 2 width (AXIe shall always report an 8 to indicate an 8-lane secondary link)

- For each slot, individual slot link connectivity

- Peripheral slot number, that is, the physical location

- Link number 1 origin (that is, the link number to the system slot)

- Link number 2 origin as "no connection"

- o Slot type

- Peripheral slot link 1 width

- Peripheral slot link 2 width shall be reported as "Not routed"

**RULE 5.14:** <Provisional addition to AXIe-2.0 Revision 2.0> System Modules that only implement AXIe-1 versions before Rev 3 shall provide a system module driver. The *PXISA\_SystemModule\_GetChassisEeprom* shall return a data structure constructed to mimic a Compact PCI EEPROM. Specifically, the following fields shall reflect the corresponding AXIe chassis information:

System Modules that support AXIe-1 Rev 3 and newer shall report:

- Vendor ID (string)

- Model (string)

- Serial Number (string)

- Slot Count (byte)

- Peripheral Slot Count (physical number of peripheral slots)

- System Slot number, that is, the physical address of the system slot (byte)

- System Slot type (AXIe shall always report a 2-Link slot type)

- System Slot Link 1 width (AXIe shall always report an 8-lane link)

- System Slot Link 2 width (AXIe shall always report an 8 to indicate an 8-lane secondary link)

- For each slot, individual slot link connectivity

- Peripheral slot number, that is, the physical location

- Link number 1 origin (that is, the link number to the system slot)

- Link number 2 origin (that is, the link number to the system slot)

- Slot type

- Peripheral slot link 1 width

- o Peripheral slot link 2 width

Note that information regarding AXIe Links 3 and 4 are not reported via this mechanism.

Details of the format for this information are in the PICMG CompactPCI specification.

#### 5.4.4 Behavior of the SMBusOperation Function

**RULE 5.15:** The system module driver *PXISA\_SystemModule\_SMBusOperation* shall not return an error although no equivalent SMBus operation is provided to the chassis.

#### 5.5 Chassis Software Requirements

In the PXI Architecture, a chassis driver is used to enumerate the PXI-1 buses in each chassis. Since an AXIe chassis manifests as a pure PXI Express chassis, AXIe chassis are not required to provide a PXI chassis driver.

**RULE 5.16:** The chassis description file for an AXIe chassis shall indicate the slot connected by the local bus connection to the left and right.

Note that for AXIe, this does not indicate the width of the connection.

The following example shows a valid descriptor of the adjacent slots to an AXIe slot:

```

[SLOT4]

LocalBusLeft = "SLOT3"

LocalBusRight = "SLOT5"

```

#### 5.5.1 An Example Chassis Description File

The following example shows a valid AXIe Chassis Description File:

```

# Example Chassis Description file.

[Chassis]

Model = "M9505a"

Vendor = "Agilent Technologies"

Slots = "1, 2, 3, 4, 5"

TriggerBusList = "1"

StarSystemTimingSetList = "1"

[TriggerBus1]

SlotList = "0,1,2,3,4,5"

[StarTrigger1]

SystemTimingSlot = 0 # ESM is part of chassis, referred to as "slot 0"

PXI STAR0 = 1

PXI STAR 1 = 2

PXI STAR 2 = 3

PXI STAR 3 = 4

PXI STAR 4 = 5

```

```

[Slot1]

LocalBusLeft = "None"

LocalBusRight = "Slot2"

[Slot2]

LocalBusLeft = "Slot1"

LocalBusRight = "Slot3"

[Slot3]

LocalBusLeft = "Slot2"

LocalBusRight = "Slot4"

[Slot4]

LocalBusLeft = "Slot3"

LocalBusRight = "Slot5"

[Slot5]

LocalBusLeft = "Slot4"

LocalBusLeft = "Slot4"

```

# 5.6 Peripheral Module Requirements

AXIe modules may include peripheral module description files. In which case, the resource manager will treat them exactly as PXI peripheral module description files.

- **RULE 5.17:** The peripheral module driver *PXISA\_PeripheralModule\_GetInformation* call shall return the actual maximum link width supported by the module, up to the AXIe imposed maximum.